# DE5a-Net

FPGA Development Kit

User Manual

#

# DE5a-NET CONTENTS

| Chapter 1                              | 5  |

|----------------------------------------|----|

| 1.1 General Description                | 5  |

| 1.2 Key Features                       | 6  |

| 1.3 Block Diagram                      | 7  |

|                                        |    |

| Chapter 2                              | 10 |

| Board Components                       | 10 |

| 2.1 Board Overview                     | 10 |

| 2.2 Configuration, Status and Setup    | 11 |

| 2.3 General User Input/Output          | 14 |

| 2.4 Temperature Sensor and Fan Control | 18 |

| 2.5 Power Monitor                      | 20 |

| 2.6 Clock Circuit                      | 21 |

| 2.7 FLASH Memory                       | 23 |

| 2.8 DDR3 SO-DIMM                       | 26 |

| 2.9 QDRII+ SRAM                        | 37 |

| 2.10 QSPF+ Ports                       | 46 |

| 2.11 PCI Express                       | 49 |

| 2-12 RS-422 Expansion Header           | 52 |

|                                        |    |

| Chapter 3                              | 54 |

| System Builder                         | 54 |

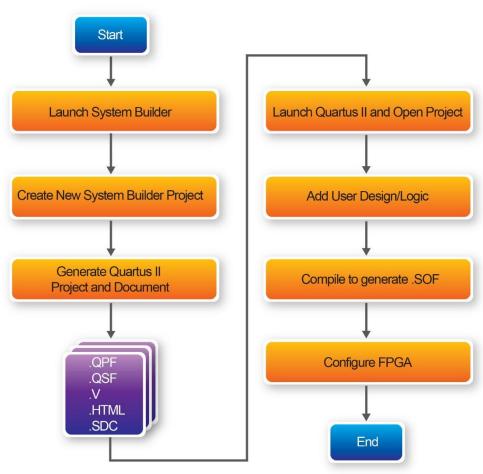

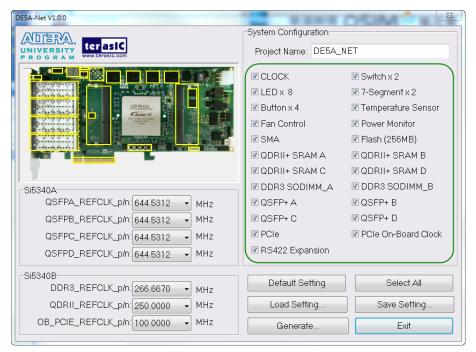

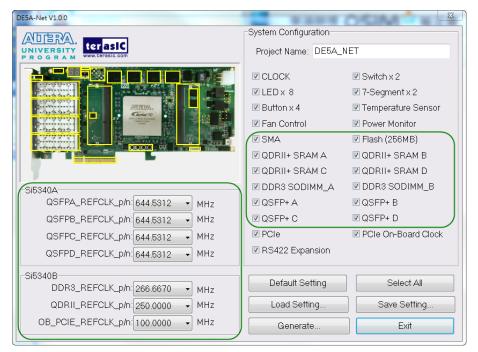

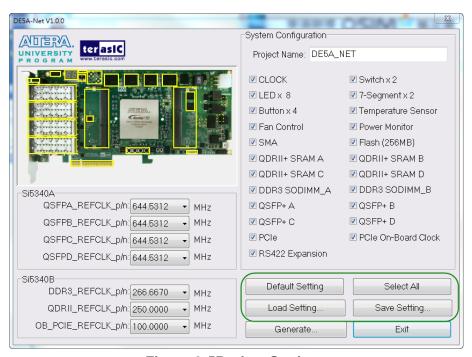

| 3.1 Introduction                       | 54 |

| 3.2 General Design Flow                | 55 |

| 3.3 Using System Builder               | 56 |

# terasic

# DE5a-NET CONTENTS

| Chapter 4                                         | 62                                      |

|---------------------------------------------------|-----------------------------------------|

| Flash Programming                                 | 62                                      |

| 4.1 CFI Flash Memory Map                          | 62                                      |

| 4.2 FPGA Configure Operation                      | 63                                      |

| 4.3 Flash Programming with Users Design           | 64                                      |

| 4.4 Restore Factory Settings                      | 65                                      |

| Chapter 5                                         | 67                                      |

| Peripheral Reference Design                       | 67                                      |

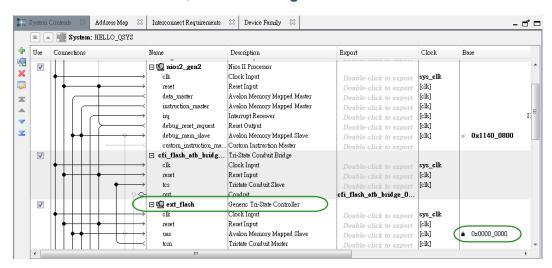

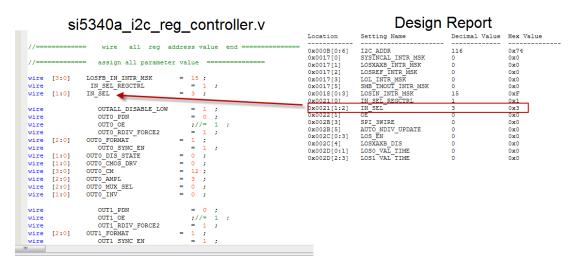

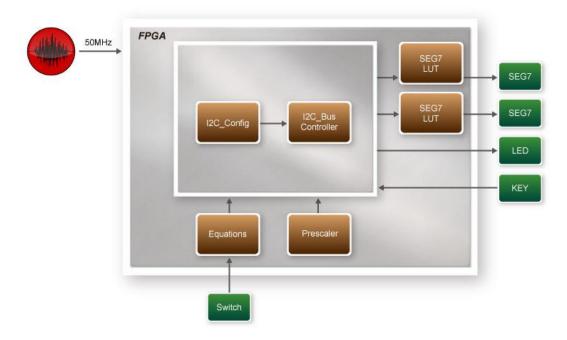

| 5.1 Configure Si5340A/B in RTL                    | 67                                      |

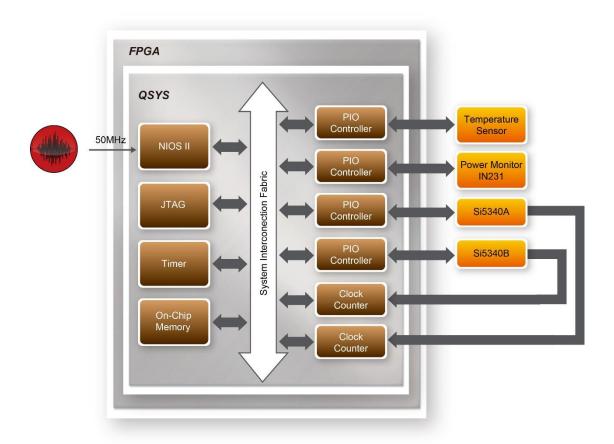

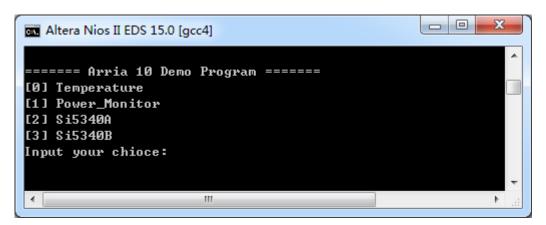

| 5.2 Nios II control for SI5340/Temperature/Power. | 76                                      |

| 5.3 Fan Speed Control                             | 81                                      |

|                                                   |                                         |

| Chapter 6                                         | 84                                      |

| Chapter 6  Memory Reference Design                |                                         |

| •                                                 | 84                                      |

| Memory Reference Design                           | 84<br>84                                |

| Memory Reference Design                           | 84<br>84<br>87                          |

| Memory Reference Design                           | 84<br>84<br>87<br>89                    |

| Memory Reference Design                           | 84<br>84<br>87<br>89                    |

| Memory Reference Design                           | 84<br>87<br>89<br><b>93</b><br>93       |

| Memory Reference Design                           | 84<br>87<br>89<br><b>93</b><br>93       |

| Memory Reference Design                           | 84<br>87<br>89<br><b>93</b><br>93       |

| Memory Reference Design                           | 84<br>87<br>89<br><b>93</b><br>93<br>94 |

# 637656

# DE5a-NET **CONTENTS**

| Chapter 8 1                               | 16  |

|-------------------------------------------|-----|

| Transceiver Verification                  |     |

| 8.1 Function of the Transceiver Test Code | 116 |

| 8.2 Loopback Fixture                      | 116 |

| 8.3 Testing                               | 118 |

|                                           |     |

| Additional Information1                   | 20  |

| Getting Help                              | 20  |

# **Chapter 1**

# **Overview**

his chapter provides an overview of the DE5a-Net Development Board and installation guide.

# 1.1 General Description

The Terasic DE5a-Net Arria 10 GX FPGA Development Kit provides the ideal hardware solution for designs that demand high capacity and bandwidth memory interfacing, ultra-low latency communication, and power efficiency. With a full-height, 3/4-length form-factor package, the DE5a-Net is designed for the most demanding high-end applications, empowered with the top-of-the-line Altera Arria 10 GX, delivering the best system-level integration and flexibility in the industry.

The Arria® 10 GX FPGA features integrated transceivers that transfer at a maximum of 12.5 Gbps, allowing the DE5a-Net to be fully compliant with version 3.0 of the PCI Express standard, as well as allowing an ultra low-latency, straight connections to four external 40G QSFP+ modules. Not relying on an external PHY will accelerate mainstream development of network applications enabling customers to deploy designs for a broad range of high-speed connectivity applications. For designs that demand high capacity and high speed for memory and storage, the DE5a-Net delivers with two independent banks of DDR3 SO-DIMM RAM, four independent banks of QDRII+ SRAM, high-speed parallel flash memory. The feature-set of the DE5a-Net fully supports all high-intensity applications such as low-latency trading, cloud computing, high-performance computing, data acquisition, network processing, and signal processing.

# **1.2 Key Features**

The following hardware is implemented on the DE5a-Net board:

#### **■** FPGA

Altera Arria® 10 GX FPGA (10AX115N3F45I2SG)

### **■** FPGA Configuration

- On-Board USB Blaster II or JTAG header for FPGA programming

- Fast passive parallel (FPPx32) configuration via MAX II CPLD and flash memory

## General user input/output:

- 8 LEDs

- 4 push-buttons

- 2 slide switches

- 2 seven-segment displays

#### Clock System

- 50MHz Oscillator

- Programmable clock generators Si5340A and Si5340B

- One SMA connector for external clock input

- One SMA connector for clock output

### Memory

- DDR3 SO-DIMM SDRAM

- QDRII+ SRAM

- FLASH

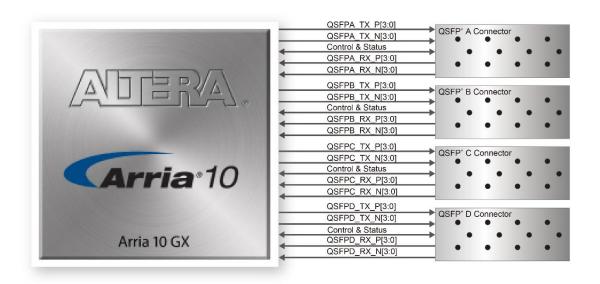

#### Communication Ports

- Four QSFP+ connectors

- PCI Express (PCIe) x8 edge connector

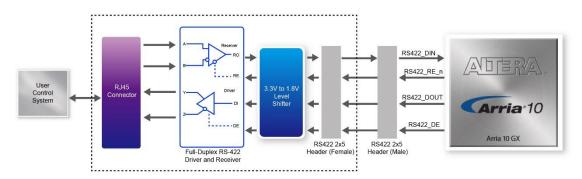

- One RS422 transceiver with RJ45 connector

# System Monitor and Control

- Temperature sensor

- Fan control

- Power monitor

#### Power

- PCI Express 6-pin power connector, 12V DC Input

- PCI Express edge connector power

## ■ Mechanical Specification

• PCI Express full-height and 3/4-length

# 1.3 Block Diagram

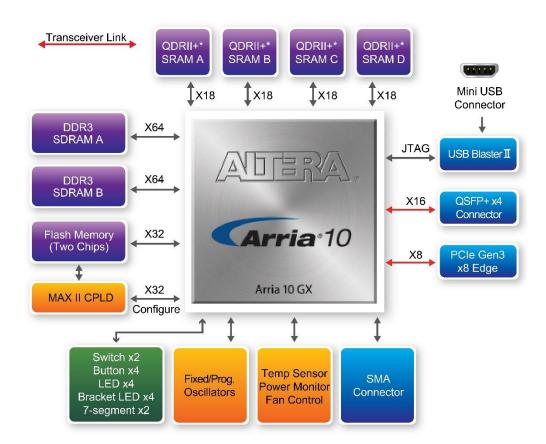

**Figure 1-1** shows the block diagram of the DE5a-Net board. To provide maximum flexibility for the users, all key components are connected with the Arria 10 GX FPGA device. Thus, users can configure the FPGA to implement any system design.

Figure 1-1 Block diagram of the DE5a-Net board

Below is more detailed information regarding the blocks in **Figure 1-1**.

#### Arria 10 GX FPGA

- 10AX115N3F45I2SG

- 1,150K logic elements (LEs)

- 67-Mbits embedded memory

- 48 transceivers (12.5Gbps)

- 3,036 18-bit x 19-bit multipliers

- 1,518 Variable-precision DSP blocks

- 4 PCI Express hard IP blocks

- 768 user I/Os

- 384 LVDS channels

- 32 phase locked loops (PLLs)

# ■ JTAG Header and FPGA Configuration

- On-board USB Blaster II or JTAG header for use with the Quartus II Programmer

- MAXII CPLD 5M2210 System Controller and Fast Passive Parallel (FPP x32) configuration

# ■ Memory devices

- 32MB QDRII+ SRAM

- Up to 8GB DDR3 SO-DIMM SDRAM for each DDR3 socket

- 256MB FLASH

#### ■ General user I/O

- 8 user controllable LEDs

- 4 user push buttons

- 2 user slide switches

- 2 seven-segment displays

#### On-Board Clock

- 50MHz oscillator

- Programming PLL providing clock for 40G QSFP+ transceiver

- Programming PLL providing clock for PCle transceiver

- Programming PLL providing clocks for DDR3 SDRAM and QDRII+ SRAM

## **■** Four QSFP+ ports

• Four QSFP+ connector (40 Gbps+)

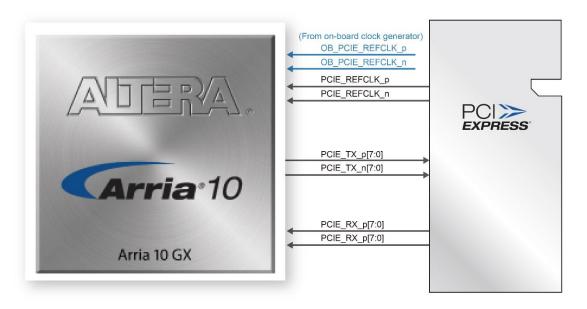

# ■ PCI Express x8 edge connector

- Support for PCle x8 Gen1/2/3

- Edge connector for PC motherboard with x8 or x16 PCI Express slot

#### **■** Power Source

- PCI Express 6-pin DC 12V power

- PCI Express edge connector power

# Chapter 2

# **Board Components**

his chapter introduces all the important components on the DE5a-Net.

## 2.1 Board Overview

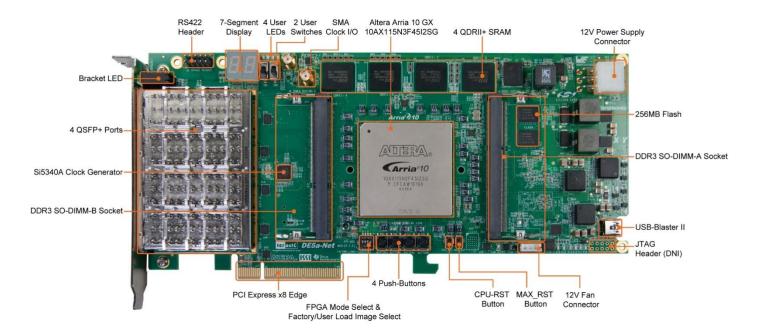

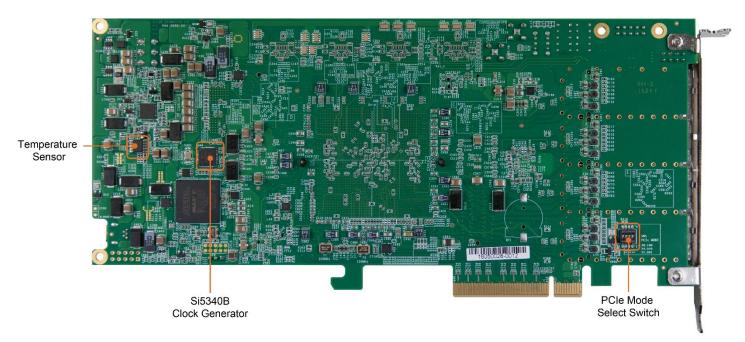

**Figure 2-1** is the top and bottom view of the DE5a-Net development board. It depicts the layout of the board and indicates the location of the connectors and key components. Users can refer to this figure for relative location of the connectors and key components.

Figure 2-1FPGABoard (Top)

Figure 2-2 FPGA Board (Bottom)

# 2.2 Configuration, Status and Setup

# **■** Configure

The FPGA board supports two configuration methods for the Arria 10 FPGA:

- Configure the FPGA using the on-board USB-Blaster II.

- Flash memory configuration of the FPGA using stored images from the flash memory on power-up.

For programming by on-board USB-Blaster II, the following procedures show how to download a configuration bit stream into the Arria 10 GX FPGA:

- Make sure that power is provided to the FPGA board

- Connect your PC to the FPGA board using a mini-USB cable and make sure the USB-Blaster II driver is installed on PC.

- Launch Quartus II programmer and make sure the USB-Blaster II is detected.

- In Quartus II Programmer, add the configuration bit stream file (.sof), check the associated "Program/Configure" item, and click "Start" to start FPGA programming.

#### ■ Status LED

The FPGA Board development board includes board-specific status LEDs to indicate board status. Please refer to **Table 2-1** for the description of the LED indicator.

Table 2-1 Status LED

| Board<br>Reference | LED Name    | Description                                                                                                                                                                    |

|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D6                 | 12-V Power  | Illuminates when 12-V power is active.                                                                                                                                         |

| D5                 | 3.3-V Power | Illuminates when 3.3-V power is active.                                                                                                                                        |

| D16                | CONF DONE   | Illuminates when the FPGA is successfully configured. Driven by the MAX II CPLD 5M2210 System Controller.                                                                      |

| D15                | Loading     | Illuminates when the MAX II CPLD 5M2210 System Controller is actively configuring the FPGA. Driven by the MAX II CPLD 5M2210 System Controller with the Embedded Blaster CPLD. |

| D17                | Error       | Illuminates when the MAX II CPLD EPM2210 System Controller fails to configure the FPGA. Driven by the MAX II CPLD EPM2210 System Controller.                                   |

| D19                | PAGE        | Illuminates when FPGA is configured by the factory configuration bit stream.                                                                                                   |

# ■ Setup PCI Express Control DIP switch

The PCI Express Control DIP switch (SW5) is provided to enable or disable different configurations of the PCIe Connector. **Table 2-2**lists the switch controls and description.

Table 2-2 SW5 PCIe Control DIP Switch

| Board<br>Reference | Signal Name      | Description                                                   | Default |

|--------------------|------------------|---------------------------------------------------------------|---------|

| SW5.1              | IPCIE PRSNT2n x1 | On: Enable x1 presence detect Off: Disable x1 presence detect | Off     |

| SW5.2              | PCIE PRSNT2n x4  | On: Enable x4 presence detect Off: Disable x4 presence detect | Off     |

| SW5.3              | PCIE_PRSNT2n_x8  | On : Enable x8 presence detect                                | On      |

Off: Disable x8 presence detect

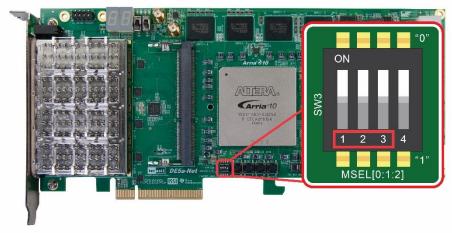

## ■ Setup Configure Mode

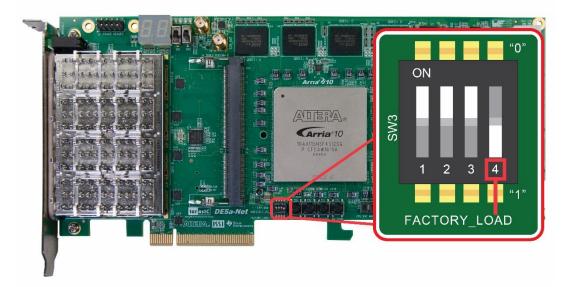

The position 1~3 of DIP switch SW3 are used to specify the configuration mode of the FPGA. As currently only one mode is supported, please set all positions as shown in **Figure 2-3**.

Figure 2-3

Position of DIP switch SW3 for Configure Mode

# ■ Select Flash Image for Configuration

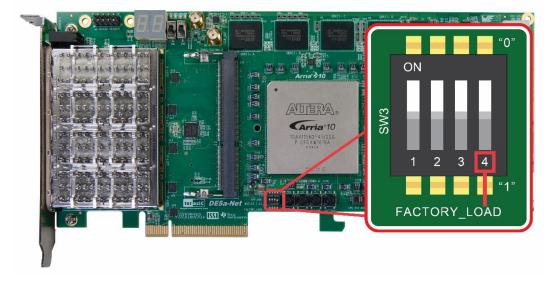

The position 4 of DIP switch SW3 is used to specify the image for configuration of the FPGA. Setting Position 4 of SW3 to "1" (down position) specifies the default factory image to be loaded, as shown in **Figure 2-4**. Setting Position 4 of SW3 to "0" (up position) specifies the DE5a-Net to load a user-defined image, as shown in **Figure 2-5**.

Figure 2-4 Position of DIP switch SW3 for Image Select – Factory Image Load

Figure 2-5 Position of DIP switch SW3 for Image Select - User Image Load

# 2.3 General User Input/Output

This section describes the user I/O interface to the FPGA.

#### ■ User Defined Push-buttons

The FPGA board includes four user defined push-buttons that allow users to interact with the Arria 10 GX device. Each push-button provides a high logic level or a low logic level when it is not pressed or pressed, respectively. **Table 2-3** lists the board

references, signal names and their corresponding Arria 10 GX device pin numbers.

Table 2-3 Push-button Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal<br>Name | Description                      | I/O<br>Standard | Arria 10 GX<br>Pin Number |

|--------------------|-----------------------------|----------------------------------|-----------------|---------------------------|

| PB0                | BUTTON0                     |                                  | 1.5-V           | PIN_AJ13                  |

| PB1                | BUTTON1                     | High Logic Level when the button | 1.5-V           | PIN_AE13                  |

| PB2                | BUTTON2                     | s not pressed                    | 1.5-V           | PIN_AV16                  |

| PB3                | BUTTON3                     |                                  | 1.5-V           | PIN_AR9                   |

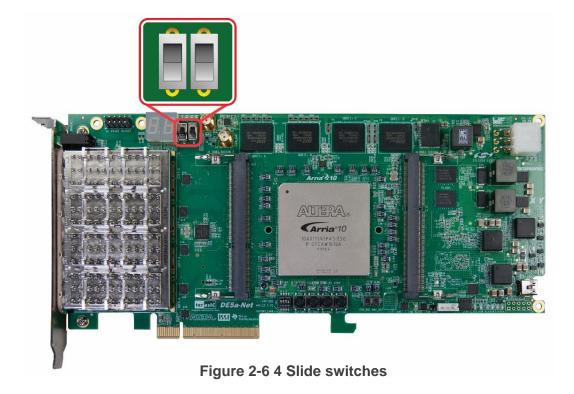

#### ■ User-Defined Slide Switch

There are two slide switches on the FPGA board to provide additional FPGA input control. When a slide switch is in the DOWN position or the UPPER position, it provides a low logic level or a high logic level to the Arria 10 GX FPGA, respectively, as shown in **Figure 2-6**.

**Table 2-4** lists the signal names and their corresponding Arria 10 GX device pin numbers.

Table 2-4 Slide Switch Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal Name | Description                     | I/O<br>Standard | Arria 10 GX<br>Pin Number |

|--------------------|--------------------------|---------------------------------|-----------------|---------------------------|

| SW0                | SW0                      | High logic level when SW in the | 1.5-V           | PIN_AY28                  |

| SW1                | SW1                      | UPPER position.                 | 1.5-V           | PIN_AM27                  |

#### ■ User-Defined LEDs

The FPGA board consists of 8 user-controllable LEDs to allow status and debugging signals to be driven to the LEDs from the designs loaded into the Arria 10 GX device. Each LED is driven directly by the Arria 10 GX FPGA. The LED is turned on or off when the associated pins are driven to a low or high logic level, respectively. A list of the pin names on the FPGA that are connected to the LEDs is given in **Table 2-5**.

Table 2-5 User LEDs Pin Assignments, Schematic Signal Names, and Functions

| Board     | Schematic    | Description                  | I/O      | Arria 10 GX Pin |

|-----------|--------------|------------------------------|----------|-----------------|

| Reference | Signal Name  | Description                  | Standard | Number          |

| D4        | LED0         |                              | 1.8-V    | PIN_T11         |

| D3        | LED1         |                              | 1.8-V    | PIN_R11         |

| D2        | LED2         | Driving a logic 0 on the I/O | 1.8-V    | PIN_N15         |

| D1        | LED3         | port turns the LED ON.       | 1.8-V    | PIN_M15         |

| D9-1      | LED_BRACKET0 | Driving a logic 1 on the I/O | 1.8-V    | PIN_AF10        |

| D9-3      | LED_BRACKET1 | port turns the LED OFF.      | 1.8-V    | PIN_AF9         |

| D9-5      | LED_BRACKET2 |                              | 1.8-V    | PIN_Y13         |

| D9-7      | LED_BRACKET3 |                              | 1.8-V    | PIN_W11         |

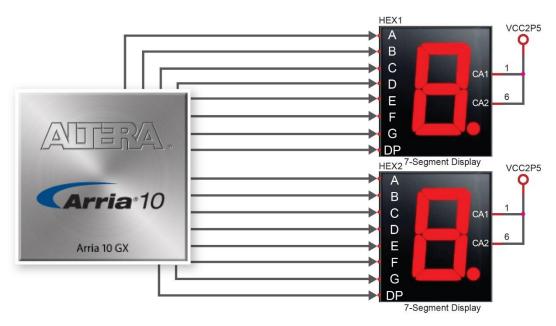

# ■ 7-Segment Displays

The FPGA board has two 7-segment displays. As indicated in the schematic in **Figure 2-7**, the seven segments are connected to pins of the Arria 10 GX FPGA. Applying a low or high logic level to a segment will turn it on or turn it off, respectively.

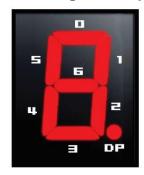

Each segment in a display is identified by an index listed from 0 to 6 with the positions given in **Figure 2-8**. In addition, the decimal point is identified as DP. **Table 2-6** shows the mapping of the FPGA pin assignments to the 7-segment displays.

Figure 2-7 Connection between 7-segment displays and Arria 10 GX FPGA

Figure 2-8 Position and index of each segment in a 7-segment display

Table 2-6 User LEDs Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal<br>Name | Description                                                                                                                              | I/O<br>Standard | Arria 10<br>GX Pin<br>Number |

|--------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------|

| HEX1               | HEX1_D0                     |                                                                                                                                          | 1.5-V           | PIN_AM33                     |

| HEX1               | HEX1_D1                     |                                                                                                                                          | 1.5-V           | PIN_AN33                     |

| HEX1               | HEX1_D2                     |                                                                                                                                          | 1.5-V           | PIN_AM32                     |

| HEX1               | HEX1_D3                     | User-Defined 7-Segment Display. Driving logic 0 on the I/O port turns the 7-segment signal ON. Driving logic 1 on the I/O port turns the | 1.5-V           | PIN_AN32                     |

| HEX1               | HEX1 D4                     |                                                                                                                                          | 1.5-V           | PIN_AN31                     |

| HEX1               | HEX1_D5                     |                                                                                                                                          | 1.5-V           | PIN_AP31                     |

| HEX1               | HEX1_D6                     | 7-segment signal OFF.                                                                                                                    | 1.5-V           | PIN_AK32                     |

| HEX1               | HEX1_DP                     | 7-3cgment signal of 1.                                                                                                                   | 1.5-V           | PIN_AK31                     |

| HEX0               | HEX0_D0                     |                                                                                                                                          | 1.5-V           | PIN_AV10                     |

| HEX0               | HEX0_D1                     |                                                                                                                                          | 1.5-V           | PIN_AV11                     |

| HEX0               | HEX0_D2                     |                                                                                                                                          | 1.5-V           | PIN_AW8                      |

| HEX0 | HEX0_D3 | 1.5-V | PIN_AY |

|------|---------|-------|--------|

| HEX0 | HEX0_D4 | 1.5-V | PIN_AY |

| HEX0 | HEX0_D5 | 1.5-V | PIN_BA |

| HEX0 | HEX0_D6 | 1.5-V | PIN_AW |

| HEX0 | HEX0_DP | 1.5-V | PIN_AW |

# 2.4 Temperature Sensor and Fan Control

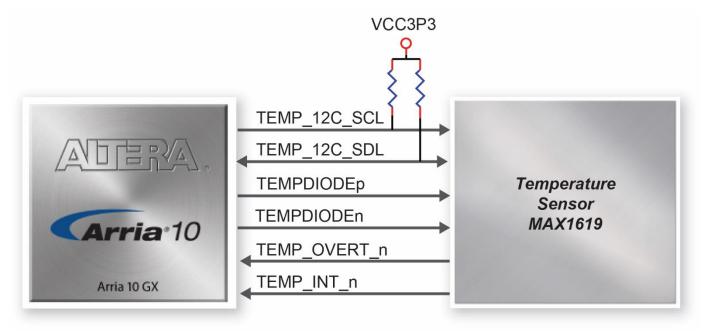

The FPGA board is equipped with a temperature sensor, MAX1619, which provides temperature sensing and over-temperature alert. These functions are accomplished by connecting the temperature sensor to the internal temperature sensing diode of the Arria 10 GX device. The temperature status and alarm threshold registers of the temperature sensor can be programmed by a two-wire SMBus, which is connected to the Arria 10 GX FPGA. In addition, the 7-bit POR slave address for this sensor is set to '0011000b'. Figure 2-9 shows the connection between the temperature sensor and the Arria 10 GX FPGA.

Figure 2-9 Connections between the temperature sensor and the Arria 10 GX FPGA

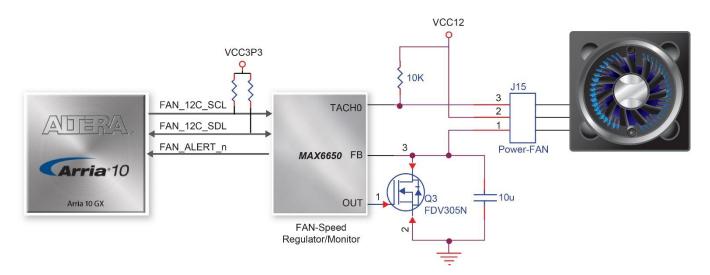

An optional 3-pin +12V fan located on J15 of the FPGA board is intended to reduce the temperature of the FPGA. The board is equipped with a Fan-Speed regulator and monitor, MAX6650, through an I2C interface, Users regulate and monitor the speed of fan depending on the measured system temperature.

Figure2-10showstheconnectionbetweenthe Fan-Speed Regulator and Monitor and the Arria 10 GX FPGA.

Figure 2-10 Connections between the Fan-Speed Regulator/ Monitor and the Arria 10 GX FPGA

The pin assignments for the associated interface are listed in **Table 2-7**.

Table 2-1Temperature Sensor and Fan Speed Control Pin Assignments, Schematic Signal Names, and Functions

| Schematic<br>Signal Name | Description                                   | I/O Standard | Arria 10 GX Pin<br>Number |

|--------------------------|-----------------------------------------------|--------------|---------------------------|

| TEMPDIODEp               | Positive pin of temperature diode in Arria 10 | -            | PIN_N21                   |

| TEMPDIODEn               | Negative pin of temperature diode in Arria 10 | -            | PIN_P21                   |

| TEMP_I2C_SCL             | SMBus clock                                   | 1.5-V        | PIN_AU12                  |

| TEMP_I2C_SDA             | SMBus data                                    | 1.5-V        | PIN_AV12                  |

| TEMP_OVERT_n             | SMBus alert (interrupt)                       | 1.5-V        | PIN_AW11                  |

| TEMP_INT_n  | SMBus alert (interrupt)    | 1.5-V | PIN_AY12 |

|-------------|----------------------------|-------|----------|

| FAN_I2C_SCL | 2-Wire Serial Clock        | 1.5-V | PIN_AJ33 |

| FAN_I2C_SDA | 2-Wire Serial-Data         | 1.5-V | PIN_AK33 |

| FAN_ALERT_n | Active-low AL<br>ERT input | 1.5-V | PIN_AL32 |

## 2.5 Power Monitor

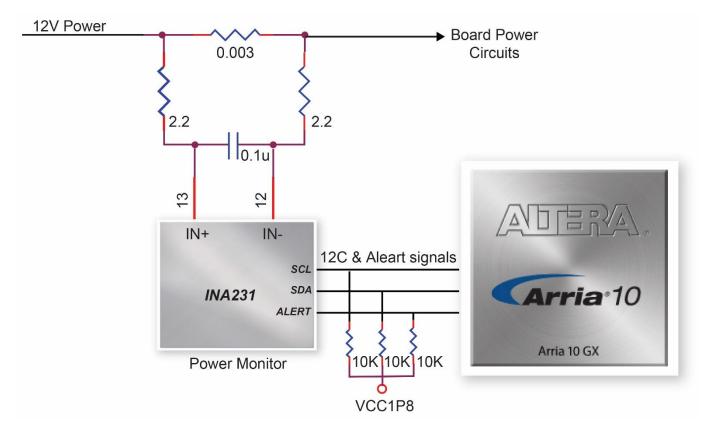

The DE5a-Net has implemented a power monitor chip to monitor the board input power voltage and current. **Figure 2-11** shows the connection between the power monitor chip and the Arria 10 GX FPGA. The power monitor chip monitors both shunt voltage drops and board input power voltage allows user to monitor the total board power consumption. Programmable calibration value, conversion times, and averaging, combined with an internal multiplier, enable direct readouts of current in amperes and power in watts. Table 2-8 shows the pin assignment of power monitor I2C bus.

Figure 2-11 Connections between the Power Monitor chip and the Arria 10 GX FPGA

| Schematic<br>Signal Name | Description         | I/O<br>Standard | Arria 10 GX<br>Pin Number |

|--------------------------|---------------------|-----------------|---------------------------|

| POWER_MONITOR_I2C_SCL    | Power Monitor SCL   | 1.8V            | PIN_AT26                  |

| POWER_MONITOR_I2C_SDA    | Power Monitor SDA   | 1.8V            | PIN_AP25                  |

| POWER_MONITOR_ALERT      | Power Monitor ALERT | 1.8V            | PIN_BD23                  |

## 2.6 Clock Circuit

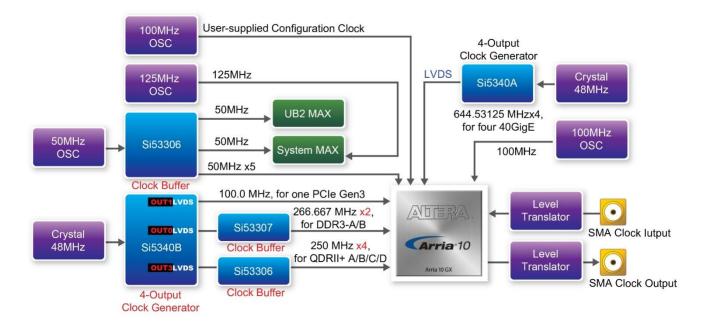

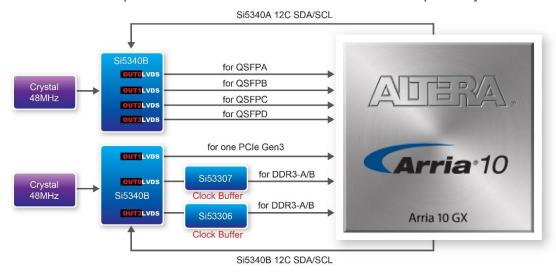

The development board includes one 50 MHz and two programmable clock generators. **Figure 2-12** shows the default frequencies of on-board all external clocks going to the Arria 10 GX FPGA.

Figure 2-12 Clock circuit of the FPGA Board

A clock buffer is used to duplicate the 50 MHz oscillator, so there are five 50MHz clocks fed into different five FPGA banks. The two programming clock generators are low-jitter oscillators which are used to provide special and high quality clock signals for high-speed transceivers and high bandwidth memory. Through I2C serial interface, the clock generator controllers in the Arria 10 GX FPGA can be used to program the Si5340A and Si5340B to generate 40G Ethernet QSFP+, PCIe and high bandwidth memory reference clocks respectively. Two SMA connectors provide external clock input and clock output respectively.

**Table2-9** lists the clock source, signal names, default frequency and their corresponding Arria 10 GX device pin numbers.

Table 2-9 Clock Source, Signal Name, Default Frequency, Pin Assignments and Functions

| Carmaa | Schematic       | Default          | I/O      | Arria 10 GX | Amuliantian                       |

|--------|-----------------|------------------|----------|-------------|-----------------------------------|

| Source | Signal Name     | Frequency        | Standard | Pin Number  | Application                       |

|        | CLK_50_B2J      |                  | 1.8V     | PIN_W36     |                                   |

|        | CLK_50_B2L      |                  | 1.8V     | PIN_H32     |                                   |

| Y1     | CLK_50_B3D      | 50.0 MHz         | 1.8V     | PIN_AN7     |                                   |

|        | CLK_50_B3F      |                  | 1.8V     | PIN_G12     |                                   |

|        | CLK_50_B3H      |                  | 1.8V     | PIN_D21     |                                   |

| Y7     | CLK_100_B3D     | 100.0MHz         | 1.8V     | PIN_AH11    |                                   |

| J2     | SMA_CLKIN       | User<br>Defined  | 1.8V     | PIN_AC32    | External Clock<br>Input           |

| J4     | SMA_CLKOUT      | User<br>Defined  | 1.8V     | PIN_AA36    | Clock Output                      |

|        | QSFPA_REFCLK_p  | 644.53125<br>MHz | LVDS     | PIN_AH5     | 40G QSFP+ A port                  |

| 1145   | QSFPB_REFCLK_p  | 644.53125<br>MHz | LVDS     | PIN_AD5     | 40G QSFP+ B<br>port               |

| U15    | QSFPC_REFCLK_p  | 644.53125<br>MHz | LVDS     | PIN_Y5      | 40G QSFP+ C<br>port               |

|        | QSFPD_REFCLK_p  | 644.53125<br>MHz | LVDS     | PIN_T5      | 40G QSFP+ D<br>port               |

|        | DDR3A_REFCLK_p  | 266.667<br>MHz   | LVDS     | PIN_AV33    | DDR3 reference clock for A port   |

| 1144   | DDR3B_REFCLK_p  | 266.667<br>MHz   | LVDS     | PIN_AP14    | DDR3 reference clock for B port   |

| U44    | QDRIIA_REFCLK_p | 250 MHz          | LVDS     | PIN_L9      | QDRII+ reference clock for A port |

|        | QDRIIB_REFCLK_p | 250 MHz          | LVDS     | PIN_N18     | QDRII+ reference clock for B port |

| l | QDRIIC_REFCLK_p  | 250 MHz    | LVDS       | PIN_G24  | QDRII+ reference |

|---|------------------|------------|------------|----------|------------------|

|   | QDNIIC_REFOLK_P  | 250 101112 | LVDS       | PIIN_G24 | clock for C port |

|   | QDRIID_REFCLK_p  | 250 MHz    | LVDS       | PIN_M34  | QDRII+ reference |

|   | QDNIID_REFOLK_P  | 250 101112 | 0 MHZ LVDS |          | clock for D port |

|   | OP DOIE DEECLY 5 | 100 MHz    | LVDS       | DIN AKAO | PCIe reference   |

| l | OB_PCIE_REFCLK_p | TOU MINZ   | LVDS       | PIN_AK40 | clock            |

**Table 2-10**lists the programmable oscillator control pins, signal names, I/O standard and their corresponding Arria 10 GX device pin numbers.

Table 2-10 Programmable oscillator control pin, Signal Name, I/O standard, Pin Assignments and Descriptions

| Programmable | Schematic       | I/O      | Arria 10 GX | Description          |

|--------------|-----------------|----------|-------------|----------------------|

| Oscillator   | Signal Name     | Standard | Pin Number  |                      |

| Si5340A      | Si5340A_I2C_SCL | 1.8-V    | PIN_AJ11    | I2C bus, connected   |

| (U15)        | Si5340A_I2C_SDA | 1.8-V    | PIN_AN8     | with Si5340A         |

|              | Si5340A_RST     | 1.8-V    | PIN_AN6     | Si5340A reset signal |

| Si5340A      | Si5340A_INTR    | 1.8-V    | PIN_AM6     | Si5340A interrupt    |

| (U15)        | 313340A_INTR    | 1.0-1    | FIIN_AIVIO  | signal               |

| (013)        | S:53404 OE n    | 1.8-V    | PIN_AJ10    | Si5340A output       |

|              | Si5340A_OE_n    | 1.0-V    | PIIN_AJIU   | enable signal        |

|              | Si5340B_I2C_SCL | 1.8-V    | PIN_G37     | I2C bus, connected   |

|              | Si5340B_I2C_SDA | 1.8-V    | PIN_H31     | with Si5340B         |

| Si5340B      | Si5340B_RST     | 1.8-V    | PIN_G38     | Si5340B reset signal |

|              | C:E240D INTD    | 101/     | DINI COO    | Si5340B interrupt    |

| (U44)        | Si5340B_INTR    | 1.8-V    | PIN_G32     | signal               |

|              | C:5240P OE n    | 1.5-V    | DINI AL 24  | Si5340B output       |

|              | Si5340B_OE_n    | 1.5-V    | PIN_AL31    | enable signal        |

# 2.7 FLASH Memory

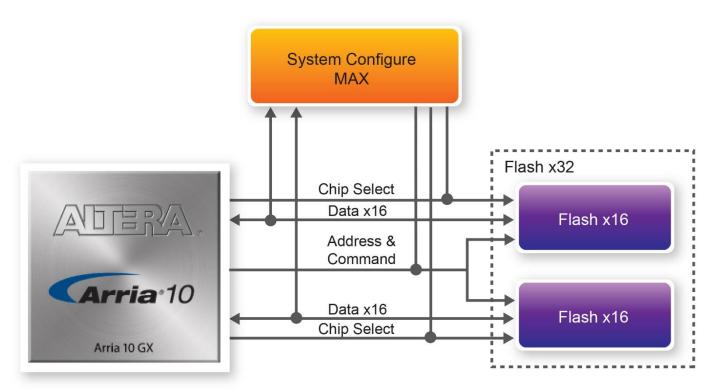

The development board has two 1Gb CFI-compatible synchronous flash devices for non-volatile storage of FPGA configuration data, user application data, and user code space.

Each interface has a 16-bit data bus and the two devices combined allow for FPP x32 configuration. This device is part of the shared flash and MAX (FM) bus, which connects to the flash memory and MAX V CPLD (5M2210) System Controller. **Figure 2-13** shows the connections between the Flash, MAX and Arria 10 GX FPGA.

Figure 2-13 Connection between the Flash, Max and Arria 10 GX FPGA

Table 2-11 lists the flash pin assignments, signal names, and functions.

Table 2-11 Flash Memory Pin Assignments, Schematic Signal Names, and Functions

| Schematic<br>Signal Name | Description | I/O Standard | Arria 10 GX Pin<br>Number |

|--------------------------|-------------|--------------|---------------------------|

| FLASH_A1                 | Address bus | 1.8-V        | PIN_H26                   |

| FLASH_A2                 | Address bus | 1.8-V        | PIN_J18                   |

| FLASH_A3                 | Address bus | 1.8-V        | PIN_N17                   |

| FLASH_A4                 | Address bus | 1.8-V        | PIN_P15                   |

| FLASH_A5                 | Address bus | 1.8-V        | PIN_B18                   |

| FLASH_A6                 | Address bus | 1.8-V        | PIN_E18                   |

| FLASH_A7                 | Address bus | 1.8-V        | PIN_D18                   |

| FLASH_A8  | Address bus | 1.8-V | PIN_J10 |

|-----------|-------------|-------|---------|

| FLASH_A9  | Address bus | 1.8-V | PIN_B17 |

| FLASH_A10 | Address bus | 1.8-V | PIN_J11 |

| FLASH_A11 | Address bus | 1.8-V | PIN_H8  |

| FLASH_A12 | Address bus | 1.8-V | PIN_A17 |

| FLASH_A13 | Address bus | 1.8-V | PIN_G8  |

| FLASH_A14 | Address bus | 1.8-V | PIN_G9  |

| FLASH_A15 | Address bus | 1.8-V | PIN_A16 |

| FLASH_A16 | Address bus | 1.8-V | PIN_K11 |

| FLASH_A17 | Address bus | 1.8-V | PIN_B15 |

| FLASH_A18 | Address bus | 1.8-V | PIN_G7  |

| FLASH_A19 | Address bus | 1.8-V | PIN_F6  |

| FLASH_A20 | Address bus | 1.8-V | PIN_A15 |

| FLASH_A21 | Address bus | 1.8-V | PIN_A14 |

| FLASH_A22 | Address bus | 1.8-V | PIN_H6  |

| FLASH_A23 | Address bus | 1.8-V | PIN_T12 |

| FLASH_A24 | Address bus | 1.8-V | PIN_U12 |

| FLASH_A25 | Address bus | 1.8-V | PIN_F7  |

| FLASH_A26 | Address bus | 1.8-V | PIN_B14 |

| FLASH_D0  | Address bus | 1.8-V | PIN_B35 |

| FLASH_D1  | Data bus    | 1.8-V | PIN_A35 |

| FLASH_D2  | Data bus    | 1.8-V | PIN_C35 |

| FLASH_D3  | Data bus    | 1.8-V | PIN_C33 |

| FLASH_D4  | Data bus    | 1.8-V | PIN_C32 |

| FLASH_D5  | Data bus    | 1.8-V | PIN_A32 |

| FLASH_D6  | Data bus    | 1.8-V | PIN_C26 |

| FLASH_D7  | Data bus    | 1.8-V | PIN_B24 |

| FLASH_D8  | Data bus    | 1.8-V | PIN_C36 |

| FLASH_D9  | Data bus    | 1.8-V | PIN_B34 |

| FLASH_D10 | Data bus    | 1.8-V | PIN_A34 |

| FLASH_D11 | Data bus    | 1.8-V | PIN_B33 |

| FLASH_D12 | Data bus    | 1.8-V | PIN_B32 |

| FLASH_D13 | Data bus    | 1.8-V | PIN_A31 |

| FLASH_D14 | Data bus    | 1.8-V | PIN_E24 |

| FLASH_D15 | Data bus    | 1.8-V | PIN_C25 |

| FLASH_D16 | Data bus    | 1.8-V | PIN_K33 |

|           |             |       |         |

| FLASH_D17              | Data bus                  | 1.8-V | PIN_J39  |

|------------------------|---------------------------|-------|----------|

| FLASH_D18              | Data bus                  | 1.8-V | PIN_AA32 |

| FLASH_D19              | Data bus                  | 1.8-V | PIN_J35  |

| FLASH_D20              | Data bus                  | 1.8-V | PIN_H36  |

| FLASH_D21              | Data bus                  | 1.8-V | PIN_AB32 |

| FLASH_D22              | Data bus                  | 1.8-V | PIN_J34  |

| FLASH_D23              | Data bus                  | 1.8-V | PIN_AA31 |

| FLASH_D24              | Data bus                  | 1.8-V | PIN_J36  |

| FLASH_D25              | Data bus                  | 1.8-V | PIN_J38  |

| FLASH_D26              | Data bus                  | 1.8-V | PIN_K34  |

| FLASH_D27              | Data bus                  | 1.8-V | PIN_H38  |

| FLASH_D28              | Data bus                  | 1.8-V | PIN_H37  |

| FLASH_D29              | Data bus                  | 1.8-V | PIN_Y31  |

| FLASH_D30              | Data bus                  | 1.8-V | PIN_H35  |

| FLASH_D31              | Data bus                  | 1.8-V | PIN_J33  |

| FLASH_CLK              | Clock                     | 1.8-V | PIN_T9   |

| FLASH_RESET_n          | Reset                     | 1.8-V | PIN_C17  |

| FLASH_CE_n[0]          | Chip enable of offlash-0  | 1.8-V | PIN_H10  |

| FLASH_CE_n[1]          | Chip enable of of flash-1 | 1.8-V | PIN_N16  |

| FLASH_OE_n             | Output enable             | 1.8-V | PIN_C16  |

| FLASH_WE_n             | Write enable              | 1.8-V | PIN_U10  |

| FLASH_ADV_n            | Address valid             | 1.8-V | PIN_H7   |

| FLASH_RDY_BSY_<br>n[0] | Ready of flash-0          | 1.8-V | PIN_J8   |

| FLASH_RDY_BSY_<br>n[1] | Ready of flash-1          | 1.8-V | PIN_L36  |

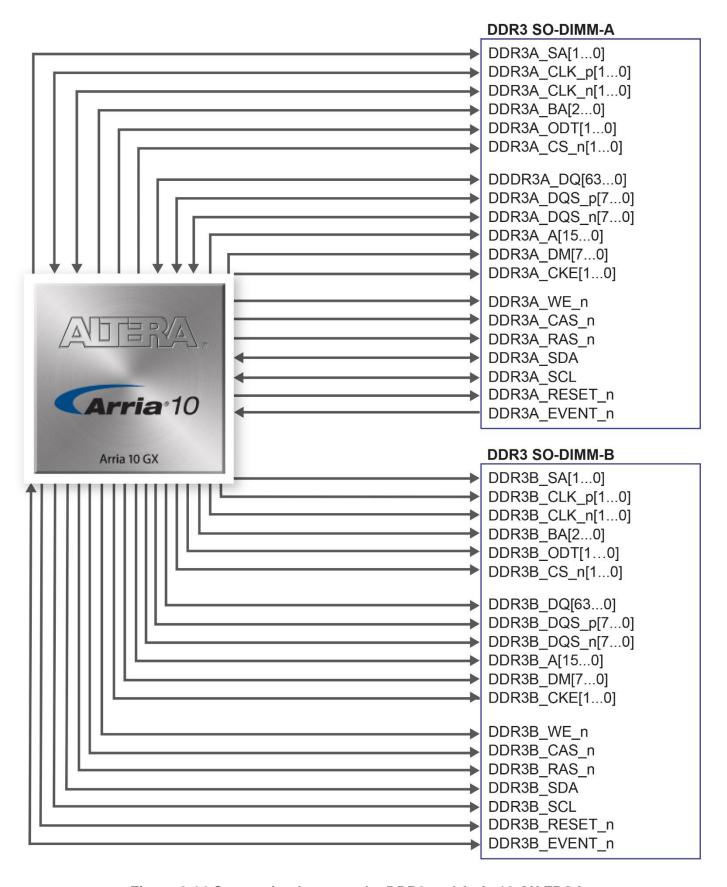

# **2.8 DDR3 SO-DIMM**

The development board supports two independent banks of DDR3 SDRAM SO-DIMM. Each DDR3 SODIMM socket is wired to support a maximum capacity of 8GB with a 64-bit data bus. Using differential DQS signaling for the DDR3 SDRAM interfaces, it is capable of running at up to 933MHz memory clock for a maximum theoretical

bandwidth up to 95.4Gbps. **Figure 2-14** shows the connections between the DDR3 SDRAM SO-DIMMs and Arria 10 GX FPGA.

Figure 2-14 Connection between the DDR3 and Arria 10 GX FPGA

The pin assignments for DDR3 SDRAM SO-DIMM Bank-A and Bank-B are listed in **Table 2-12** and **Table 2-13**, in respectively.

Table 2-12 DDR3-A Bank Pin Assignments, Schematic Signal Names, and Functions

| Schematic   | Description | I/O Standard   | Arria 10 GX Pin |

|-------------|-------------|----------------|-----------------|

| Signal Name |             | ii o otarraara | Number          |

| DDR3A_DQ0   | Data [0]    | SSTL-15        | PIN_AH32        |

| DDR3A_DQ1   | Data [1]    | SSTL-15        | PIN_AH33        |

| DDR3A_DQ2   | Data [2]    | SSTL-15        | PIN_AJ34        |

| DDR3A_DQ3   | Data [3]    | SSTL-15        | PIN_AG35        |

| DDR3A_DQ4   | Data [4]    | SSTL-15        | PIN_AH35        |

| DDR3A_DQ5   | Data [5]    | SSTL-15        | PIN_AJ35        |

| DDR3A_DQ6   | Data [6]    | SSTL-15        | PIN_AJ36        |

| DDR3A_DQ7   | Data [7]    | SSTL-15        | PIN_AH36        |

| DDR3A_DQ8   | Data [8]    | SSTL-15        | PIN_AN35        |

| DDR3A_DQ9   | Data [9]    | SSTL-15        | PIN_AP34        |

| DDR3A_DQ10  | Data [10]   | SSTL-15        | PIN_AM35        |

| DDR3A_DQ11  | Data [11]   | SSTL-15        | PIN_AL35        |

| DDR3A_DQ12  | Data [12]   | SSTL-15        | PIN_AM37        |

| DDR3A_DQ13  | Data [13]   | SSTL-15        | PIN_AT34        |

| DDR3A_DQ14  | Data [14]   | SSTL-15        | PIN_AL36        |

| DDR3A_DQ15  | Data [15]   | SSTL-15        | PIN_AK36        |

| DDR3A_DQ16  | Data [16]   | SSTL-15        | PIN_AU35        |

| DDR3A_DQ17  | Data [17]   | SSTL-15        | PIN_AT36        |

| DDR3A_DQ18  | Data [18]   | SSTL-15        | PIN_AU37        |

| DDR3A_DQ19  | Data [19]   | SSTL-15        | PIN_AV37        |

| DDR3A_DQ20  | Data [20]   | SSTL-15        | PIN_AV35        |

| DDR3A_DQ21  | Data [21]   | SSTL-15        | PIN_AV36        |

| DDR3A_DQ22  | Data [22]   | SSTL-15        | PIN_AT39        |

| DDR3A_DQ23  | Data [23]   | SSTL-15        | PIN_AU39        |

| DDR3A_DQ24  | Data [24]   | SSTL-15        | PIN_AR36        |

| DDR3A_DQ25  | Data [25]   | SSTL-15        | PIN_AN36        |

| DDR3A_DQ26  | Data [26]   | SSTL-15        | PIN_AN38        |

| DDR3A_DQ27  | Data [27]   | SSTL-15        | PIN_AN37        |

| DDR3A_DQ28  | Data [28]   | SSTL-15        | PIN_AM38        |

| DDR3A_DQ29 | Data [29]        | SSTL-15            | PIN_AM39 |

|------------|------------------|--------------------|----------|

| DDR3A_DQ30 | Data [30]        | SSTL-15            | PIN_AR37 |

| DDR3A_DQ31 | Data [31]        | SSTL-15            | PIN_AR39 |

| DDR3A_DQ32 | Data [32]        | SSTL-15            | PIN_AL30 |

| DDR3A_DQ33 | Data [33]        | SSTL-15            | PIN_AM30 |

| DDR3A_DQ34 | Data [34]        | SSTL-15            | PIN_AP28 |

| DDR3A_DQ35 | Data [35]        | SSTL-15            | PIN_AN28 |

| DDR3A_DQ36 | Data [36]        | SSTL-15            | PIN_AN30 |

| DDR3A_DQ37 | Data [37]        | SSTL-15            | PIN_AN27 |

| DDR3A_DQ38 | Data [38]        | SSTL-15            | PIN_AM28 |

| DDR3A_DQ39 | Data [39]        | SSTL-15            | PIN_AM29 |

| DDR3A_DQ40 | Data [40]        | SSTL-15            | PIN_BB32 |

| DDR3A_DQ41 | Data [41]        | SSTL-15            | PIN_BA32 |

| DDR3A_DQ42 | Data [42]        | SSTL-15            | PIN_BB30 |

| DDR3A_DQ43 | Data [43]        | SSTL-15            | PIN_BC31 |

| DDR3A_DQ44 | Data [44]        | SSTL-15            | PIN_AY29 |

| DDR3A_DQ45 | Data [45]        | SSTL-15            | PIN_AY31 |

| DDR3A_DQ46 | Data [46]        | SSTL-15            | PIN_AW29 |

| DDR3A_DQ47 | Data [47]        | SSTL-15            | PIN_AW28 |

| DDR3A_DQ48 | Data [48]        | SSTL-15            | PIN_BC30 |

| DDR3A_DQ49 | Data [49]        | SSTL-15            | PIN_BD30 |

| DDR3A_DQ50 | Data [50]        | SSTL-15            | PIN_BB29 |

| DDR3A_DQ51 | Data [51]        | SSTL-15            | PIN_BB28 |

| DDR3A_DQ52 | Data [52]        | SSTL-15            | PIN_BD28 |

| DDR3A_DQ53 | Data [53]        | SSTL-15            | PIN_BD29 |

| DDR3A_DQ54 | Data [54]        | SSTL-15            | PIN_BC27 |

| DDR3A_DQ55 | Data [55]        | SSTL-15            | PIN_BB27 |

| DDR3A_DQ56 | Data [56]        | SSTL-15            | PIN_AT27 |

| DDR3A_DQ57 | Data [57]        | SSTL-15            | PIN_AU27 |

| DDR3A_DQ58 | Data [58]        | SSTL-15            | PIN_AT30 |

| DDR3A_DQ59 | Data [59]        | SSTL-15            | PIN_AR28 |

| DDR3A_DQ60 | Data [60]        | SSTL-15            | PIN_AU29 |

| DDR3A_DQ61 | Data [61]        | SSTL-15            | PIN_AV28 |

| DDR3A_DQ62 | Data [62]        | SSTL-15            | PIN_AT29 |

| DDR3A_DQ63 | Data [63]        | SSTL-15            | PIN_AR27 |

| DDR3A_DQS0 | Data Strobe p[0] | Differential 1.5-V | PIN_AK37 |

|            |                  |                    |          |

|              |                  | SSTL                       |          |

|--------------|------------------|----------------------------|----------|

| DDR3A_DQS_n0 | Data Strobe n[0] | Differential 1.5-V<br>SSTL | PIN_AL37 |

| DDR3A_DQS1   | Data Strobe p[1] | Differential 1.5-V<br>SSTL | PIN_AL34 |

| DDR3A_DQS_n1 | Data Strobe n[1] | Differential 1.5-V<br>SSTL | PIN_AM34 |

| DDR3A_DQS2   | Data Strobe p[2] | Differential 1.5-V<br>SSTL | PIN_AU38 |

| DDR3A_DQS_n2 | Data Strobe n[2] | Differential 1.5-V<br>SSTL | PIN_AV38 |

| DDR3A_DQS3   | Data Strobe p[3] | Differential 1.5-V<br>SSTL | PIN_AP38 |

| DDR3A_DQS_n3 | Data Strobe n[4] | Differential 1.5-V<br>SSTL | PIN_AR38 |

| DDR3A_DQS4   | Data Strobe p[4] | Differential 1.5-V<br>SSTL | PIN_AP29 |

| DDR3A_DQS_n4 | Data Strobe n[4] | Differential 1.5-V<br>SSTL | PIN_AR29 |

| DDR3A_DQS5   | Data Strobe p[5] | Differential 1.5-V<br>SSTL | PIN_BA29 |

| DDR3A_DQS_n5 | Data Strobe n[5] | Differential 1.5-V<br>SSTL | PIN_BA30 |

| DDR3A_DQS6   | Data Strobe p[6] | Differential 1.5-V<br>SSTL | PIN_BA26 |

| DDR3A_DQS_n6 | Data Strobe n[6] | Differential 1.5-V<br>SSTL | PIN_BA27 |

| DDR3A_DQS7   | Data Strobe p[7] | Differential 1.5-V<br>SSTL | PIN_AV30 |

| DDR3A_DQS_n7 | Data Strobe n[7] | Differential 1.5-V<br>SSTL | PIN_AW30 |

| DDR3A_DM0    | Data Mask [0]    | SSTL-15                    | PIN_AK34 |

| DDR3A_DM1    | Data Mask [1]    | SSTL-15                    | PIN_AP35 |

| DDR3A_DM2    | Data Mask [2]    | SSTL-15                    | PIN_AT37 |

| DDR3A_DM3    | Data Mask [3]    | SSTL-15                    | PIN_AP36 |

| DDR3A_DM4    | Data Mask [4]    | SSTL-15                    | PIN_AP30 |

| DDR3A_DM5    | Data Mask [5]    | SSTL-15                    | PIN_BA31 |

| Data Mask [6]            | SSTL-15                                                                                                                                                                                                                                                                                                                                                                                                                                | PIN_BD31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Mask [7]            | SSTL-15                                                                                                                                                                                                                                                                                                                                                                                                                                | PIN_AU30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [0]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_AW34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [1]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_AY34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [2]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_AV31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [3]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_AW31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [4]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_BA37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [5]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_BB37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [6]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_AY36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [7]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_AY37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address [8]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_AY32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

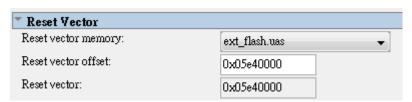

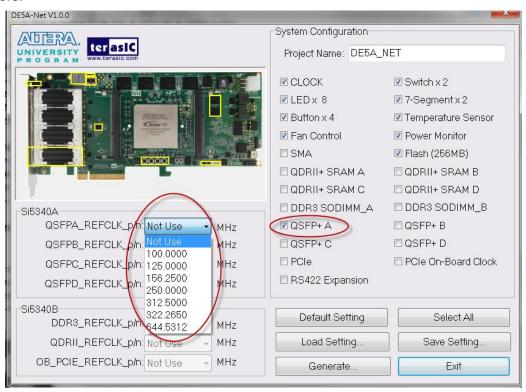

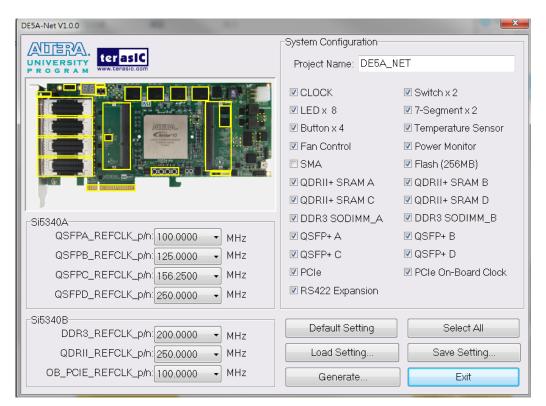

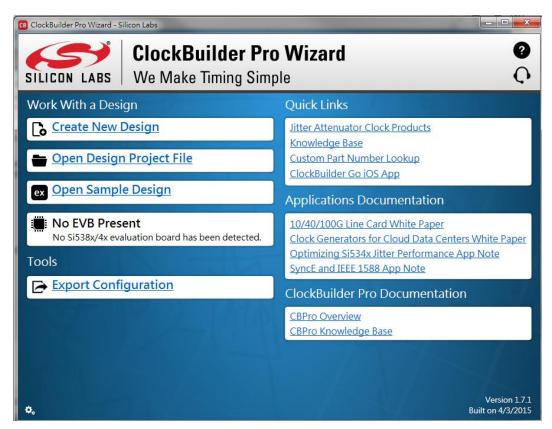

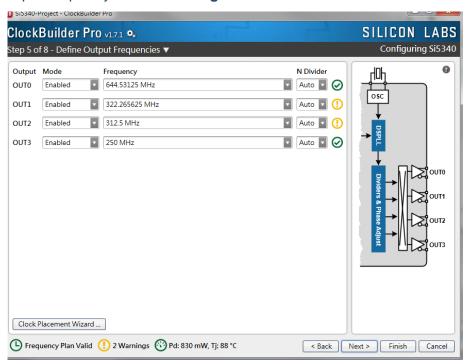

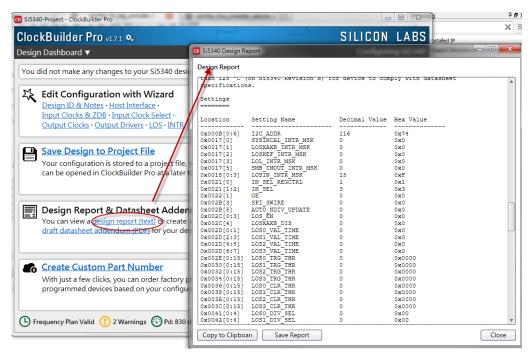

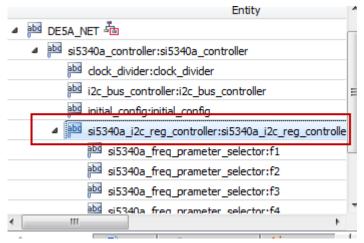

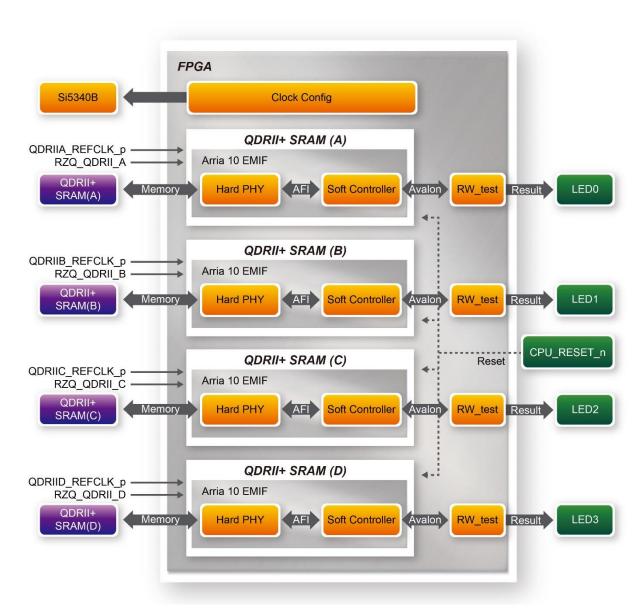

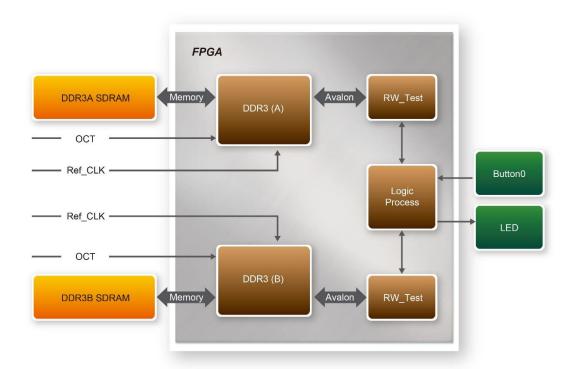

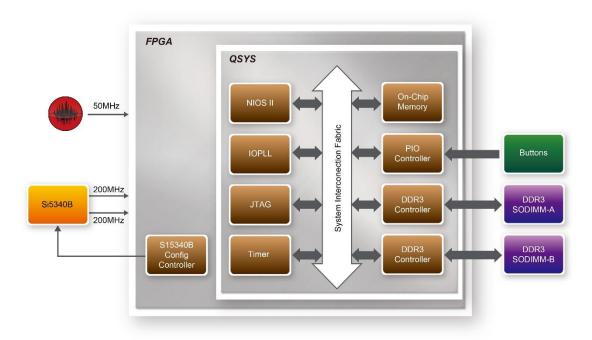

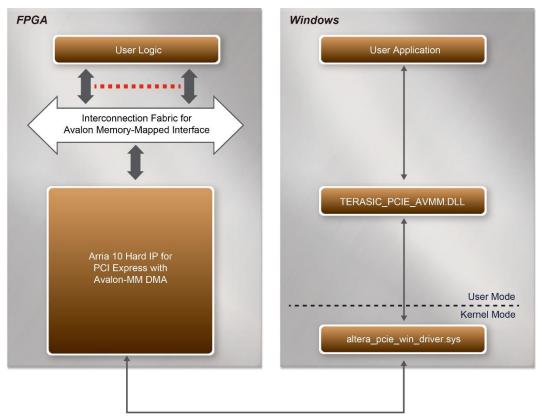

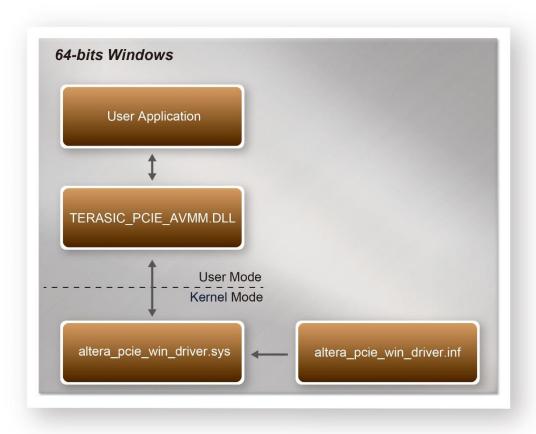

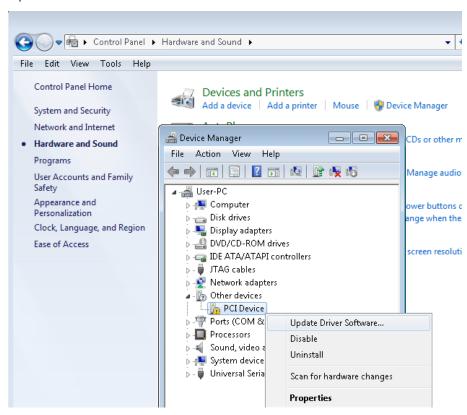

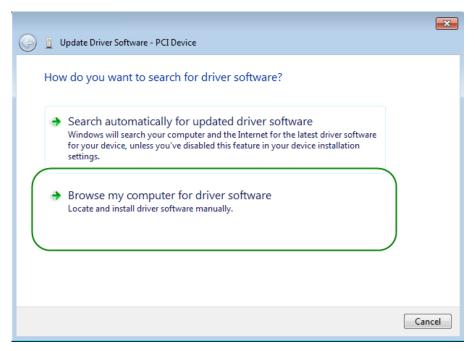

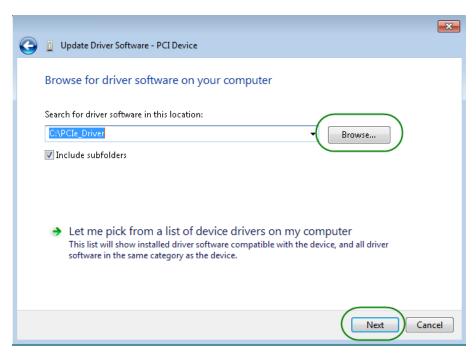

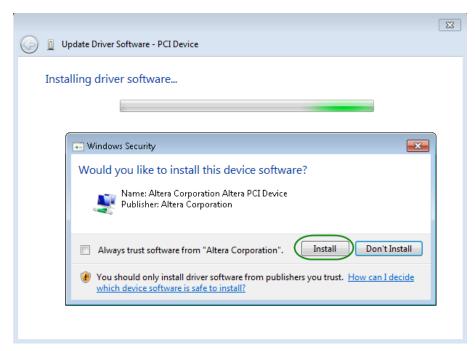

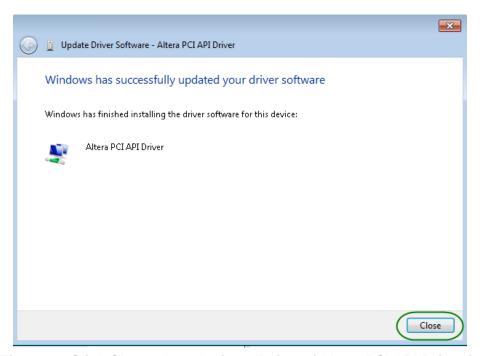

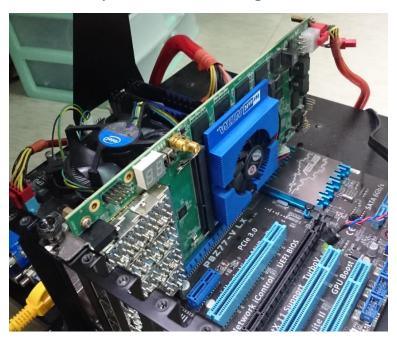

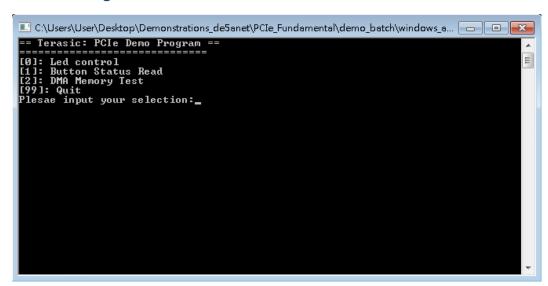

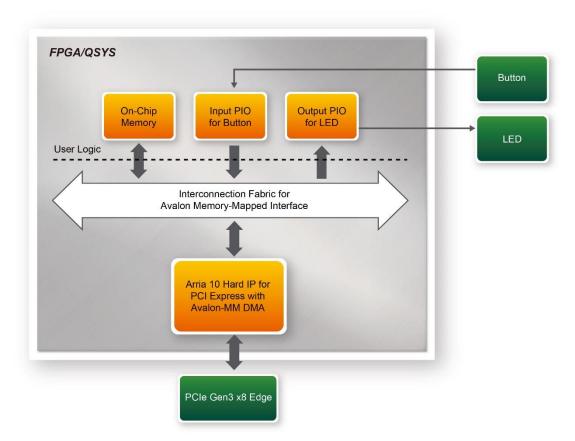

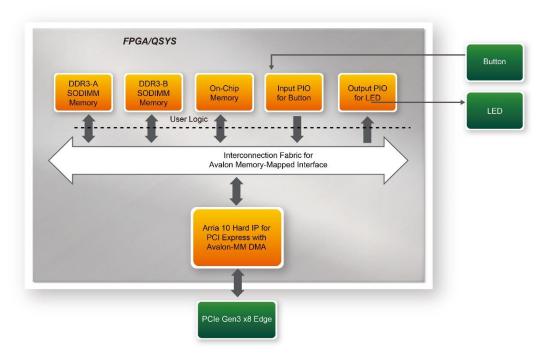

| Address [9]              | SSTL-15 Class I                                                                                                                                                                                                                                                                                                                                                                                                                        | PIN_AY33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |