# ARM<sup>®</sup> Versatile<sup>™</sup> Express Cortex<sup>®</sup>-M Prototyping Systems (V2M-MPS2 and V2M-MPS2+)

**Technical Reference Manual**

# ARM<sup>®</sup> Versatile<sup>™</sup> Express Cortex<sup>®</sup>-M Prototyping Systems (V2M-MPS2 and V2M-MPS2+)

#### **Technical Reference Manual**

Copyright © 2013-2016 ARM. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue    | Date             | Confidentiality  | Change               |

|----------|------------------|------------------|----------------------|

| DDI0525A | 20 December 2013 | Non-Confidential | First issue of TRM   |

| DDI0525B | 1 October 2014   | Non-Confidential | Second issue of TRM  |

| DDI0525C | 10 November 2014 | Non-Confidential | Third issue of TRM   |

| 0100-03  | 2 April 2015     | Non-Confidential | Fourth issue of TRM  |

| 0200-04  | 2 September 2015 | Non-Confidential | Fifth issue of TRM   |

| 0200-05  | 11 January 2016  | Non-Confidential | Sixth issue of TRM   |

| 0200-06  | 18 July 2016     | Non-Confidential | Seventh issue of TRM |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with <sup>®</sup> or <sup>TM</sup> are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at *http://www.arm.com/about/trademark-usage-guidelines.php*

Copyright © 2013-2016, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

http://www.arm.com

#### **Conformance Notices**

#### **Federal Communications Commission Notice**

This device is test equipment and consequently is exempt from part 15 of the FCC Rules under section 15.103 (c).

# CE Declaration of Conformity

The system should be powered down when not in use.

It is recommended that ESD precautions be taken when handling Versatile<sup>™</sup> Express boards.

The motherboard generates, uses, and can radiate radio frequency energy and may cause harmful interference to radio communications. There is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures:

- Ensure attached cables do not lie across the target board

- · Reorient the receiving antenna

- · Increase the distance between the equipment and the receiver

- · Connect the equipment into an outlet on a circuit different from that to which the receiver is connected

- · Consult the dealer or an experienced radio/TV technician for help

----- Note ------

It is recommended that wherever possible shielded interface cables be used.

# Contents ARM<sup>®</sup> Versatile<sup>™</sup> Express Cortex<sup>®</sup>-M Prototyping Systems (V2M-MPS2 and V2M-MPS2+) Technical Reference Manual

| Pref                 | ace                                                                                               |                                    |  |  |

|----------------------|---------------------------------------------------------------------------------------------------|------------------------------------|--|--|

|                      | About this book                                                                                   | 7                                  |  |  |

|                      | Feedback                                                                                          | 10                                 |  |  |

| Introduction         |                                                                                                   |                                    |  |  |

| 1.1                  | Precautions                                                                                       | 1-12                               |  |  |

| 1.2                  | About the Versatile <sup>™</sup> Express V2M-MPS2 and V2M-MPS2+ motherboards                      | 1-14                               |  |  |

| 1.3                  | Location of components on the V2M-MPS2 motherboard                                                | 1-15                               |  |  |

| 1.4                  | Location of components on the V2M-MPS2+ motherboard                                               | 1-18                               |  |  |

| Hardware Description |                                                                                                   |                                    |  |  |

| 2.1                  | Overview of the V2M-MPS2 and V2M-MPS2+ hardware                                                   | 2-21                               |  |  |

| 2.2                  | Clocks                                                                                            | 2-24                               |  |  |

| 2.3                  | Powerup, powerdown, and resets                                                                    | 2-26                               |  |  |

| 2.4                  | User expansion port                                                                               | 2-27                               |  |  |

| 2.5                  | USB 2.0 Full Speed interface                                                                      | 2-28                               |  |  |

| 2.6                  | SPI interface                                                                                     | 2-29                               |  |  |

| 2.7                  | UART interface                                                                                    | 2-30                               |  |  |

| 2.8                  | VGA and CLCD interfaces                                                                           | 2-31                               |  |  |

| 2.9                  | Audio interface                                                                                   | 2-32                               |  |  |

|                      | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>Harc<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8 | <ul> <li>1.1 Precautions</li></ul> |  |  |

|              | 2.10                | Ethernet interface                                |           |  |  |

|--------------|---------------------|---------------------------------------------------|-----------|--|--|

|              | 2.11                | User switches and user LEDs                       | 2-34      |  |  |

|              | 2.12                | External user memory                              | 2-35      |  |  |

|              | 2.13                | MCC FPGA serial interface                         | 2-38      |  |  |

|              | 2.14                | Power                                             |           |  |  |

|              | 2.15                | Debug and trace                                   |           |  |  |

|              | 2.16                | Overview of FPGA debug and trace systems          |           |  |  |

|              | 2.17                | Minimum design settings for motherboard operation |           |  |  |

| Chapter 3    | Configuration       |                                                   |           |  |  |

|              | 3.1                 | Overview of the configuration process             |           |  |  |

|              | 3.2                 | Configuration system                              |           |  |  |

|              | 3.3                 | Powerup and configuration process                 |           |  |  |

|              | 3.4                 | Reset push buttons                                |           |  |  |

|              | 3.5                 | Configuration files                               | 3-55      |  |  |

| Chapter 4    | Programmers Model   |                                                   |           |  |  |

|              | 4.1                 | About this programmers model                      |           |  |  |

|              | 4.2                 | Memory map                                        |           |  |  |

|              | 4.3                 | Register summary                                  |           |  |  |

|              | 4.4                 | SCC register descriptions                         | 4-62      |  |  |

|              | 4.5                 | System configuration registers                    |           |  |  |

| Chapter 5    | Signal Descriptions |                                                   |           |  |  |

|              | 5.1                 | Debug connectors                                  | 5-73      |  |  |

|              | 5.2                 | Expansion connectors                              |           |  |  |

|              | 5.3                 | CLCD connector                                    | 5-81      |  |  |

|              | 5.4                 | USB 2.0 connector                                 | 5-83      |  |  |

|              | 5.5                 | UART connector                                    | 5-84      |  |  |

|              | 5.6                 | SPI connector                                     | 5-85      |  |  |

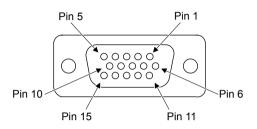

|              | 5.7                 | VGA connector                                     | 5-86      |  |  |

|              | 5.8                 | Audio connectors                                  | 5-87      |  |  |

|              | 5.9                 | Ethernet connector                                | 5-88      |  |  |

|              | 5.10                | 12V power connector                               | 5-89      |  |  |

| Appendix A.1 | Specifications      |                                                   |           |  |  |

|              | A.1.1               | Electrical specification                          | Аррх-А-91 |  |  |

| Appendix B.2 | Revisions           |                                                   |           |  |  |

|              | B.2.1               | Revisions                                         | Аррх-В-94 |  |  |

# Preface

This preface introduces the  $ARM^{\otimes}$  Versatile<sup>TM</sup> Express Cortex<sup> $\otimes$ </sup>-M Prototyping Systems (V2M-MPS2 and V2M-MPS2+) Technical Reference Manual.

It contains the following:

- *About this book* on page 7.

- Feedback on page 10.

### About this book

This book describes the ARM<sup>®</sup> Versatile<sup>™</sup> Express Cortex<sup>®</sup>-M Prototyping Systems, that is, the V2M-MPS2 and V2M-MPS2+ motherboards. Previous issues of this book had document number DDI0525.

#### Product revision status

The *rmpn* identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rm Identifies the major revision of the product, for example, r1.

- pn Identifies the minor revision or modification status of the product, for example, p2.

#### Intended audience

This book is written for experienced hardware and software engineers who are doing ARM M-Class processor evaluation and development using the Versatile<sup>™</sup> Express Cortex<sup>®</sup>-M Prototyping System, on either the V2M-MPS2 or V2M-MPS2+ motherboard.

#### Using this book

This book is organized into the following chapters:

#### **Chapter 1 Introduction**

This chapter provides an introduction to the Versatile Express Cortex-M Prototyping Systems. Two versions are available, the V2M-MPS2 and V2M-MPS2+ motherboards.

#### **Chapter 2 Hardware Description**

This chapter describes the Versatile Express V2M-MPS2 and V2M-MPS2+ motherboard hardware.

#### **Chapter 3 Configuration**

This chapter describes the powerup and configuration process of the Versatile Express V2M-MPS2 and V2M-MPS2+ motherboards.

#### **Chapter 4 Programmers Model**

This chapter describes the programmers model of the Versatile Express V2M-MPS2 and V2M-MPS2+ motherboards.

#### **Chapter 5 Signal Descriptions**

This chapter describes the signals present at the interface connectors of the Versatile Express V2M-MPS2 and V2M-MPS2+ motherboards

#### Appendix A.1 Specifications

This chapter contains the electrical specification of the Versatile Express V2M-MPS2 and V2M-MPS2+ motherboards and FPGAs.

#### Appendix B.2 Revisions

This chapter describes the technical changes between released issues of this book.

#### Glossary

The ARM Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See the ARM Glossary for more information.

#### **Typographic conventions**

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value. **monospace bold**

Denotes language keywords when used outside example code.

#### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode\_2>

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *ARM glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

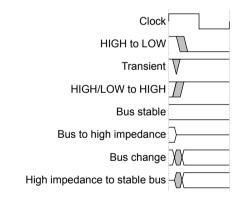

#### **Timing diagrams**

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Figure 1 Key to timing diagram conventions

#### Signals

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name denotes an active-LOW signal.

#### Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

#### **ARM** publications

- Cortex<sup>®</sup>-M0+ Technical Reference Manual (ARM DDI 0484)

- Cortex<sup>®</sup>-M0 Technical Reference Manual (ARM DDI 0432)

- Cortex<sup>®</sup>-M1 FPGA Development Kit Cortex-M1 User Guide: Altera Edition v1.1 (ARM DUI 0395)

- Cortex<sup>®</sup>-M1 FPGA Development Kit v1.1: Installation Guide (ARM DSI 0048)

- Cortex<sup>®</sup>-M1 Technical Reference Manual (ARM DDI 0413)

- Cortex<sup>®</sup>-M3 Technical Reference Manual (ARM DDI 0337)

- Cortex<sup>®</sup>-M3 Devices Generic User Guide (ARM DUI 0552)

- Cortex<sup>®</sup>-M4 Technical Reference Manual (ARM DDI 0439)

- Cortex<sup>®</sup>-M4 Devices Generic User Guide (ARM DUI 0553)

- Cortex<sup>®</sup>-M System Design Kit Technical Reference Manual (ARM DDI 0479)

- Application Note AN382 ARM<sup>®</sup> Cortex<sup>®</sup>-M0 SMM on V2M MPS2 (ARM DAI 0382)

- Application Note AN383 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ SMM on V2M-MPS2 (ARM DAI 0383)

- Application Note AN384 ARM<sup>®</sup> Cortex<sup>®</sup>-M1 SMM on V2M-MPS2 (ARM DAI 0384)

- Application Note AN385 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 SMM on V2M-MPS2 (ARM DAI 0385)

- Application Note AN386 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 SMM on V2M-MPS2 (ARM DAI 0386)

- Application Note AN387 ARM<sup>®</sup> Cortex<sup>®</sup>-M0 Design Start SMM on V2M-MPS2 (ARM DAI 0387)

- Application Note AN399 ARM<sup>®</sup> Cortex<sup>®</sup>-M7 SMM on V2M-MPS2 (ARM DAI 0399)

- Application Note AN400 ARM<sup>®</sup> Cortex<sup>®</sup>-M7CS SMM on V2M-MPS2 (ARM DAI 0400)

- Application Note AN502 Adapter for Arduino (ARM DAI 0502)

- Cortex<sup>®</sup>-M1 FPGA Development Kit Example System Tutorial: Altera Cyclone III Edition (ARM DUI 0430)

- ARM DSTREAM System and Interface Design Reference (ARM DUI 0499)

- ARM DSTREAM Setting up the Hardware (ARM DUI 0481)

- *ARM DSTREAM and RVI Using the Debug Hardware Configuration Utilities* (ARM DUI 0498)

- ARM CoreSight<sup>™</sup> Components Technical Reference Manual (ARM DDI 0314)

#### Other publications

• See the Altera website *http://altera.com* for information on the Altera Cyclone 5CEA7 FPGA and the Altera Cyclone 5CEA9 FPGA.

# Feedback

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to *errata@arm.com*. Give:

- The title *ARM*<sup>®</sup> *Versatile*<sup>™</sup> *Express Cortex*<sup>®</sup>-*M Prototyping Systems (V2M-MPS2 and V2M-MPS2+) Technical Reference Manual.*

- The number ARM 100112 0200 06 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

— Note —

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 Introduction

This chapter provides an introduction to the Versatile Express Cortex-M Prototyping Systems. Two versions are available, the V2M-MPS2 and V2M-MPS2+ motherboards.

It contains the following sections:

- 1.1 Precautions on page 1-12.

- 1.2 About the Versatile<sup>™</sup> Express V2M-MPS2 and V2M-MPS2+ motherboards on page 1-14.

- 1.3 Location of components on the V2M-MPS2 motherboard on page 1-15.

- 1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

### 1.1 **Precautions**

You can take certain precautions to ensure safety and prevent damage to your V2M-MPS2 or V2M-MPS2+ motherboard.

This section contains the following subsections:

- 1.1.1 Ensuring safety on page 1-12.

- *1.1.2 Operating temperature* on page 1-12.

- *1.1.3 Preventing damage* on page 1-12.

- *1.1.4 Encryption key* on page 1-12.

#### 1.1.1 Ensuring safety

An on-board connector supplies 12V DC to the motherboard.

——— Warning ——

- Do not use the motherboard near equipment that is sensitive to electromagnetic emissions, for example, medical equipment.

- Any external 12V DC +/- 10% power supply that is used must be a limited power source.

#### 1.1.2 Operating temperature

The V2M-MPS2 and V2M-MPS2+ motherboards have been tested in the temperature range 15°C to 30°C.

#### 1.1.3 Preventing damage

The motherboard is intended for use within a laboratory or engineering development environment. The board is sensitive to electrostatic discharges and permits electromagnetic emissions.

—— Caution —

To avoid damage to the motherboard, observe the following precautions:

- You must connect the external power supply to the board before powerup to prevent damage.

- Never subject the board to high electrostatic potentials. Observe Electrostatic Discharge (ESD) precautions when handling any board.

- Always wear a grounding strap when handling the board.

- Only hold the board by the edges.

- Avoid touching the component pins or any other metallic element except the metal shielding for the connectors.

- Avoid contact with components on the board which might be hot or sharp.

- Ensure that the voltage on the pins of the FPGA and interface circuitry on the board is at the correct level.

- You must not configure as outputs any FPGA pins that connect directly to other outputs or an external signal source.

- Do not use the board near a transmitter of electromagnetic emissions.

#### 1.1.4 Encryption key

ARM supplies the V2M-MPS2 and V2M-MPS2+ motherboards with encryption keys programmed into the FPGAs.

A battery supplies power to part of the FPGA that stores the AES decryption key. You use this key to enable loading of encrypted images.

— Caution -

The decryption key is lost when this part of the FPGA loses power. If this happens, you must return the board to ARM for reprogramming of the decryption key.

# 1.2 About the Versatile<sup>™</sup> Express V2M-MPS2 and V2M-MPS2+ motherboards

The V2M-MPS2 and V2M-MPS2+ motherboards are development platforms for ARM Cortex-M evaluation and development.

The V2M-MPS2 and V2M-MPS2+ motherboards provide the following:

#### Altera Cyclone FPGA and board powerup and configuration

The V2M-MPS2 motherboard provides an Altera Cyclone 5CEA7 FPGA, and the V2M-MPS2+ motherboard provides an Altera Cyclone 5CEA9 FPGA, both speed grade C8. Both motherboards support ARM Cortex-M software evaluation and development. A *Motherboard Configuration Controller* (MCC) supports board powerup and configuration. An on-board EEPROM stores board and file identification information and a microSD card stores FPGA and software images and configuration files. You can access the microSD card to perform configuration file editing and to update FPGA and software images.

—— Caution ——

Images that are created for the Altera Cyclone 5CEA7 FPGA are not compatible with the Altera Cyclone 5CEA9 FPGA. Images that are created for the Altera Cyclone 5CEA9 FPGA are not compatible with the Altera Cyclone 5CEA7 FPGA.

#### External user memory

On-board external SSRAM and PSRAM connect to memory interfaces in the FPGA.

#### Access ports

The V2M-MPS2 and V2M-MPS2+ motherboards provide access through Ethernet, general-purpose UART, and SPI ports. A general-purpose user expansion port supports user expansion to extra signal or bus I/O.

#### Video and audio output

The V2M-MPS2 and V2M-MPS2+ motherboards provide video output through VGA and CLCD ports. The CLCD port drives an LCD module that is configured for SPI graphics and I<sup>2</sup>C touch screen. Input and output audio ports connect to a stereo audio codec which connects to an I<sup>2</sup>S digital audio interface on the FPGA.

#### User LEDs and user switches

The V2M-MPS2 and V2M-MPS2+ motherboards provide user LEDs, an 8-way dip switch and push buttons that connect to the FPGA and to the MCC. The meaning of these LEDs and push buttons depend on the image that you implement in the FPGA.

#### System LEDs

The V2M-MPS2 and V2M-MPS2+ motherboards provide LEDs which denote *Configuration Complete*, *MCC Powered*, *Ethernet Duplex Link Established*, *Ethernet Link Operating at 100Mbs*, *Ethernet Link Established*, and *microSD Card Read or Write Access*.

#### Debug

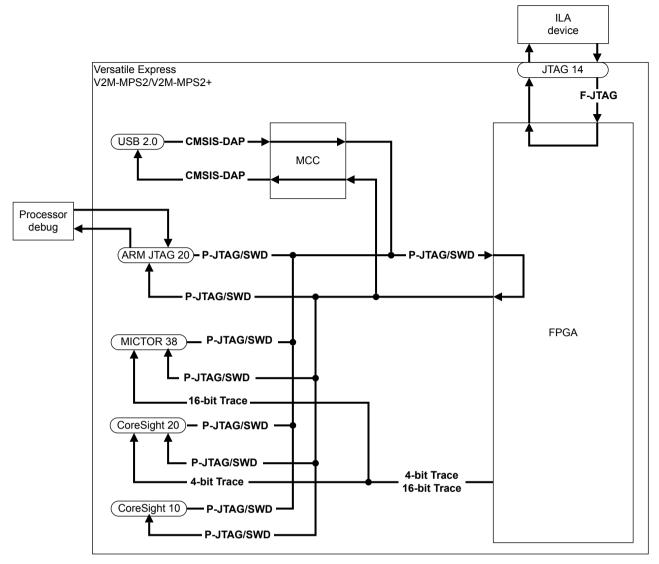

The V2M-MPS2 and V2M-MPS2+ motherboards support P-JTAG Processor debug, F-JTAG *Integrated Logic Analyzer* (ILA) FPGA debug, 4-bit trace and 16-bit trace debug, and CMSIS-DAP FPGA debug.

\_\_\_\_\_ Note \_\_\_\_\_

The V2M-MPS2 and V2M-MPS2+ motherboards require motherboard configuration controller firmware version 2.0.1 or later to support CMSIS-DAP FPGA debug.

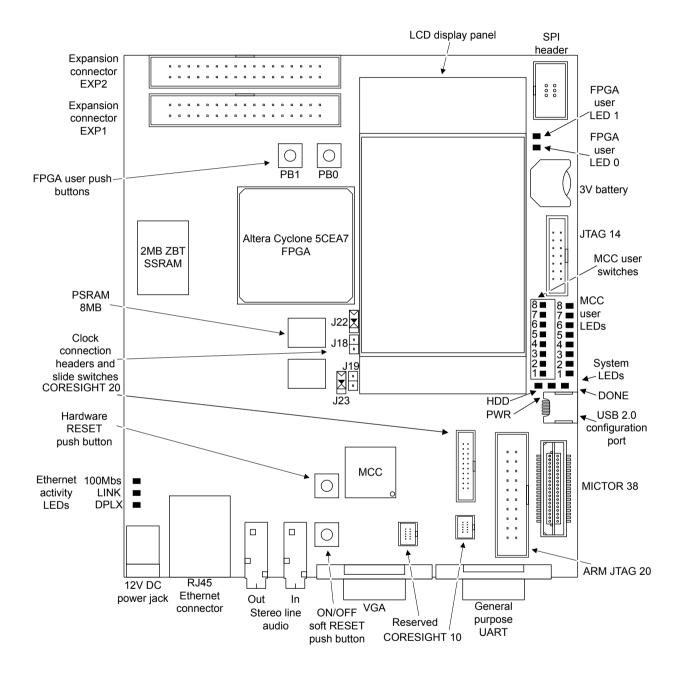

# 1.3 Location of components on the V2M-MPS2 motherboard

The following figure shows the upper face of the V2M-MPS2 motherboard.

Figure 1-1 Upper face of the V2M-MPS2 motherboard.

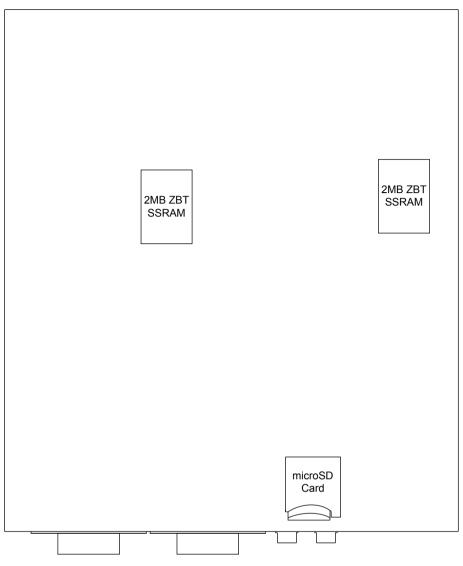

The following figure shows the lower face of the V2M-MPS2 motherboard.

Figure 1-2 Lower face of the V2M-MPS2 motherboard.

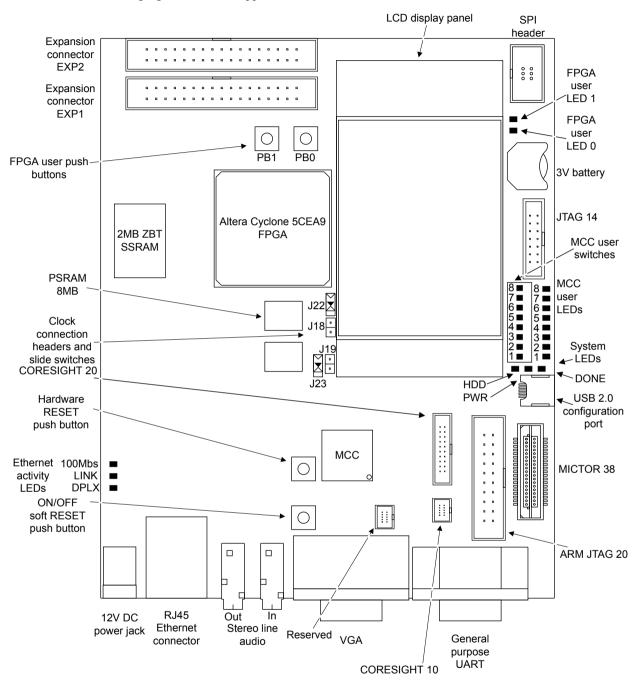

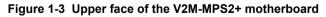

# 1.4 Location of components on the V2M-MPS2+ motherboard

The following figure shows the upper face of the V2M-MPS2+ motherboard.

The following figure shows the lower face of the V2M-MPS2+ motherboard.

Figure 1-4 Lower face of the V2M-MPS2+ motherboard.

# Chapter 2 Hardware Description

This chapter describes the Versatile Express V2M-MPS2 and V2M-MPS2+ motherboard hardware.

It contains the following sections:

- 2.1 Overview of the V2M-MPS2 and V2M-MPS2+ hardware on page 2-21.

- 2.2 Clocks on page 2-24.

- 2.3 Powerup, powerdown, and resets on page 2-26.

- 2.4 User expansion port on page 2-27.

- 2.5 USB 2.0 Full Speed interface on page 2-28.

- 2.6 SPI interface on page 2-29.

- 2.7 UART interface on page 2-30.

- 2.8 VGA and CLCD interfaces on page 2-31.

- 2.9 Audio interface on page 2-32.

- 2.10 Ethernet interface on page 2-33.

- 2.11 User switches and user LEDs on page 2-34.

- 2.12 External user memory on page 2-35.

- 2.13 MCC FPGA serial interface on page 2-38.

- 2.14 Power on page 2-41.

- 2.15 Debug and trace on page 2-42.

- 2.16 Overview of FPGA debug and trace systems on page 2-43.

- 2.17 Minimum design settings for motherboard operation on page 2-47.

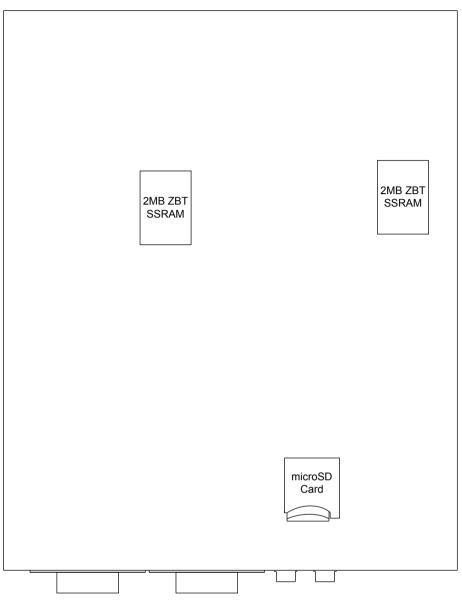

# 2.1 Overview of the V2M-MPS2 and V2M-MPS2+ hardware

The hardware infrastructure supports ARM M-class processor evaluation and development, system expansion, and debug interfaces.

The following figure shows the high-level hardware infrastructure.

The V2M-MPS2 and V2M-MPS2+ motherboards contain the following components and interfaces:

- One Altera Cyclone 5CEA7 FPGA on the V2M-MPS2 motherboard:

Speed grade C8.

- One Altera Cyclone 5CEA9 FPGA on the V2M-MPS2+ motherboard:

Speed grade C8.

- External user system memory for Cortex-M processors:

- Two 32-bit 2MB ZBT SSRAM with independent 32-bit memory interfaces.

- One 64-bit 4MB ZBT SSRAM:

- Two 32-bit 2MB ZBT SSRAM connected as one 4MB 64-bit memory.

- Two 16-bit 8MB PSRAM to supplement ZBT SSRAM.

- One MCC that supports board configuration at powerup or reset:

- FPGA configuration.

- Clock generator configuration.

- Board configuration.

- Pre-loading of SRAM images.

- Loading of *Real Time Clock* (RTCC) registers.

- CMSIS-DAP FPGA debug through the USB 2.0 port.

- One microSD card that stores the following:

- FPGA images.

- Software images.

- Board configuration files.

- On-board clock generators:

- One fixed 25MHz clock for Ethernet MAC/PHY.

- Three programmable system clocks.

- Two crystals for MCC.

- Real Time Clock (RTC) in MCC:

- Powered by 3V lithium coin cell battery.

- I<sup>2</sup>S digital audio output:

- IDC expansion ports:

- Ethernet port.

- UART.

- SPI interface.

- Video output:

- VGA output.

- CLCD output with SPI interface.

- USB 2.0 Full Speed port that supports:

— USB memory access to the microSD card for *Drag-and-Drop* configuration file editing.

- User switches and user LEDs:

- Two green LEDs and two push buttons that connect to the FPGA.

- Eight green LEDs and one 8-way dip switch that connect to the MCC.

- System LEDs:

- DONE green LED that denotes board powerup and configuration complete.

- *PWR* green LED that denotes MCC powered up and active.

- HDD green LED that flashes during access to microSD card.

- *LINK* green LED that denotes Ethernet activity.

- *DPLX* green LED that denotes Ethernet connection operating in duplex mode.

- 100Mbs green LED that denotes Ethernet connection operating at 10Mbs or 100Mbs.

- Debug and trace interfaces:

- ARM JTAG 20 connector that supports P-JTAG Processor debug and SWD.

- CoreSight<sup>™</sup> 10 connector that supports P-JTAG Processor debug and SWD.

- CoreSight<sup>™</sup> 20 connector that supports P-JTAG Processor debug, SWD, and 4-bit trace.

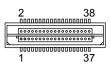

- MICTOR 38 connector that supports P-JTAG Processor debug, SWD, and 16-bit trace.

- JTAG 14 connector that supports F-JTAG FPGA debug.

- USB 2.0 Full Speed port that supports CMSIS-DAP FPGA debug.

#### — Note –

- The availability of P-JTAG, SWD, 4-bit trace or 16-bit trace, F-JTAG FPGA debug or CMSIS-DAP FPGA debug depends on the design which you implement in the FPGA.

- CMSIS-DAP debug accesses the FPGA on the same bus as P-JTAG/SWD.

- The V2M-MPS2 and V2M-MPS2+ motherboards require motherboard configuration controller firmware version 2.0.1 or later to support CMSIS-DAP.

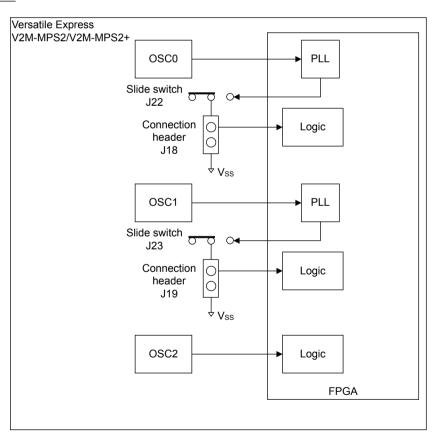

# 2.2 Clocks

The V2M-MPS2 and V2M-MPS2+ motherboards each provide three programmable on-board clock generators.

#### **Overview of clocks**

Three clock generators on the V2M-MPS2 and V2M-MPS2+ motherboards and other clock generators inside the FPGA generate the clocks that the board uses. The MCC configures the programmable clock generators during powerup sequencing using values that the configuration files define.

You configure the frequencies of the on-board clock generators by editing the OSCLKS section of the application note .txt file in the microSD card.

You can bypass the on-board clock generators and import external clocks to the MCC board using the connection headers that the V2M-MPS2 and V2M-MPS2+ motherboards provide.

The following figure shows the clocks on the V2M-MPS2 and V2M-MPS2+ motherboards. The figure shows two of the clock generators that connect to PLLs inside the FPGA with external loopback to logic inside the FPGA. The third clock generator connects directly to logic inside the FPGA.

– Note –

- The slide switches and connection headers are for general-purpose use. You can use them for any purpose whatsoever according to the needs of the design which you implement in the FPGA.

- The availability of clock generators and logic in the FPGA depend on the design which you implement in the FPGA.

#### Figure 2-2 Motherboard clocks

#### **Related concepts**

3.5.2 config.txt generic motherboard configuration file on page 3-56.

#### **Related references**

1.3 Location of components on the V2M-MPS2 motherboard on page 1-15. 1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

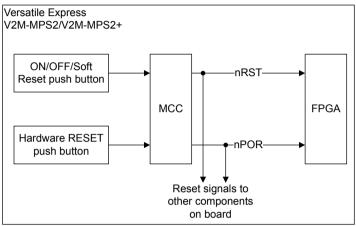

### 2.3 Powerup, powerdown, and resets

The two reset push buttons generate the reset request signals on the V2M-MPS2 and V2M-MPS2+ motherboards.

When you press one of the reset push buttons, *Hardware RESET* button or *ON/OFF/Soft RESET* button, the MCC generates appropriate signals to reset the system.

The MCC asserts **nRST** after a reset request from the *ON/OFF/Soft RESET* button. Optionally, when you set *ASSERTNPOR* to TRUE in the config.txt file, the MCC also asserts **nPOR**.

The following figure shows the powerup *ON/OFF/Soft RESET* and *Hardware RESET* push-button signals in the system.

\_\_\_\_\_ Note \_\_\_\_\_

- The board labels the ON/OFF/Soft RESET push button as nPBON.

- The board labels the *Hardware RESET* push button as *nCFGRST*.

The V2M-MPS2 and V2M-MPS2+ motherboards perform a full system configuration at powerup.

#### **Related concepts**

3.3 Powerup and configuration process on page 3-52.3.5.2 config.txt generic motherboard configuration file on page 3-56.

#### **Related references**

1.3 Location of components on the V2M-MPS2 motherboard on page 1-15. 1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

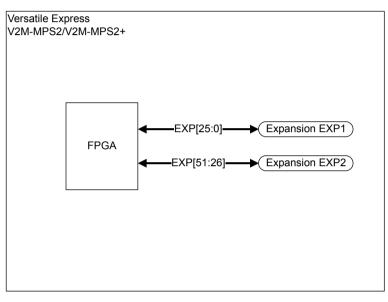

# 2.4 User expansion port

The V2M-MPS2 and V2M-MPS2+ motherboards support expansion to add user functionality.

#### Overview of the user expansion port

Two IDC headers support general-purpose user expansion.

The general-purpose headers provide:

- Six 3V volt power pins:

- The 3V supply can supply up to 300mA total through the six power pins.

- 52 general-purpose I/O signals.

Figure 2-4 Motherboard user expansion port

The Arduino Adapter Board, available from ARM, supports connectivity to up to two Arduino form factor shield boards. See *Application Note AN502 Adapter for Arduino* for information on the Arduino Adapter Board.

#### **Related references**

5.2 Expansion connectors on page 5-79.

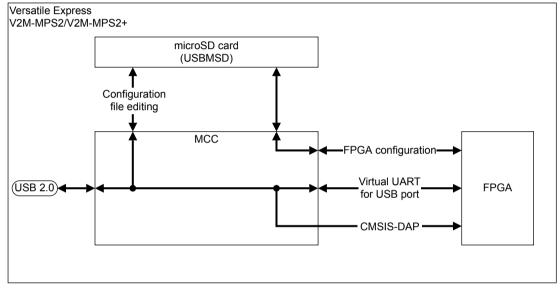

# 2.5 USB 2.0 Full Speed interface

The V2M-MPS2 and V2M-MPS2+ motherboards provide one USB 2.0 Full Speed interface that connects to the MCC.

In the standby state or during runtime, the USB 2.0 Full Speed interface supports memory access to the microSD card for *Drag-and-Drop* configuration file editing. The motherboard then uses the updated files during the configuration process.

During runtime, the USB 2.0 Full Speed interface supports:

- Virtual UART access to the FPGA through a connection between the MCC and the FPGA.

- CMSIS-DAP FPGA debug through a connection between the MCC and the FPGA.

The following figure shows the USB 2.0 Full Speed interface.

Figure 2-5 Motherboard USB 2.0 Full Speed interface

The designs that ARM supplies do not implement virtual UART access to the FPGA. If you implement the virtual UART, you must make the following pin assignments in the FPGA to enable the virtual UART to operate.

assign CLCD\_PDH[10] = uart\_txd; assign uart\_rxd\_mcu\_i = CLCD\_PDH[11];

After configuration, the board uses the FPGA configuration interface as the SCC and SPI interface.

#### **Related concepts**

- Note

- Note

3.1 Overview of the configuration process on page 3-49.

- 3.2 Configuration system on page 3-51.

- 3.5.1 Overview of configuration files and microSD card directory structure on page 3-55.

- 2.16.6 CMSIS-DAP FPGA debug on page 2-46.

#### **Related references**

5.4 USB 2.0 connector on page 5-83.

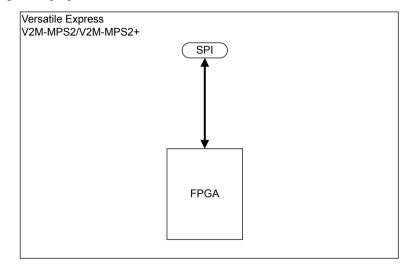

# 2.6 SPI interface

The V2M-MPS2 and V2M-MPS2+ motherboards provides access to a general-purpose SPI interface from the FPGA.

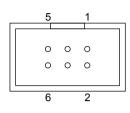

The following figure shows the general-purpose SPI interface.

#### **Related references**

5.6 SPI connector on page 5-85.

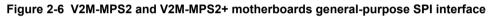

# 2.7 UART interface

The V2M-MPS2 and V2M-MPS2+ motherboards provide access to a general-purpose UART interface from the FPGA in Data Communications Equipment (DCE) configuration.

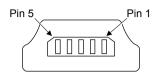

The following figure shows the general-purpose UART interface.

#### **Related references**

5.5 UART connector on page 5-84.

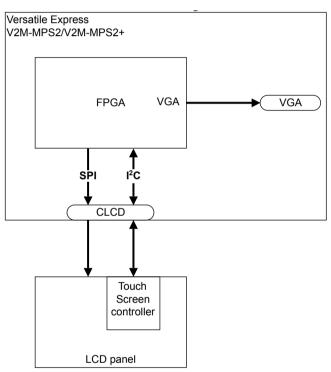

# 2.8 VGA and CLCD interfaces

The V2M-MPS2 and V2M-MPS2+ motherboards support VGA and CLCD video output.

#### Overview of the VGA interface

The VGA interface consists of a VGA controller in the FPGA, a passive resistor network, and an output VGA port. The VGA output has 4 bits per channel color depth.

#### Overview of the CLCD interface

The CLCD interface consists of an SPI bus that is connected between the FPGA and a CLCD connector and an LCD touch screen.

The LCD *Thin Film Technology* (TFT) display panel is fitted to the CLCD connector and has 320x240 pixel resolution. The panel includes a 4-wire resistive touch screen and an STEMPE811 touch screen controller that is connected to the FPGA over an I<sup>2</sup>C bus.

The following figure shows the motherboard VGA and CLCD interfaces.

Figure 2-8 VGA and CLCD interfaces.

#### LCD panel

The LCD panel is configured for SPI graphics and I<sup>2</sup>C touch-screen.

### **Related references**

- 1.3 Location of components on the V2M-MPS2 motherboard on page 1-15.

- 1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

- 5.3 CLCD connector on page 5-81.

- 5.7 VGA connector on page 5-86.

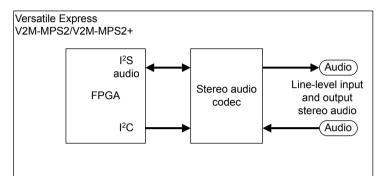

# 2.9 Audio interface

The V2M-MPS2 and V2M-MPS2+ motherboards provide a stereo line-level input and a stereo line-level output.

The audio interface consists of an audio controller in the FPGA, a low-power audio codec, and input and output stereo audio ports. The audio controller configures the codec over an  $I^2C$  bus. The FPGA and codec send audio data to each other over an  $I^2S$  bus.

The following diagram shows the audio interface.

Figure 2-9 Audio interface

### **Related references**

5.8 Audio connectors on page 5-87.

- 1.3 Location of components on the V2M-MPS2 motherboard on page 1-15.

- 1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

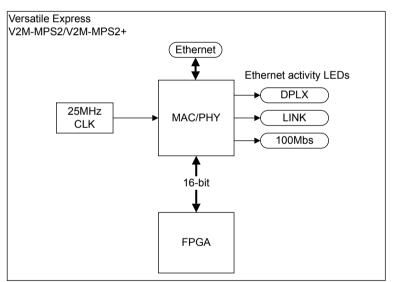

# 2.10 Ethernet interface

The V2M-MPS2 and V2M-MPS2+ motherboards provide an Ethernet MAC interface.

#### Overview of the Ethernet interface.

The Ethernet interface consists of a 16-bit interface on the FPGA, a combined Ethernet MAC and PHY on the board, and Ethernet connector for external connection.

\_\_\_\_\_ Note \_\_\_\_\_

The MAC/PHY connects to the same 16-bit interface as the 16MB PSRAM external memory.

The V2M-MPS2 and V2M-MPS2+ motherboards contain three LEDs that denote Ethernet activity:

- LINK LED:

- On denotes Ethernet connection established.

- Off denotes Ethernet connection not established.

- DPLX LED:

- On denotes connection operating in duplex mode.

- Off denotes Ethernet connection operating in simplex mode

- 100Mbs LED:

- On denotes Ethernet connection operating at 100Mbs.

- Off denotes Ethernet connection operating at 10Mbs.

The following diagram shows the Ethernet interface.

Figure 2-10 Ethernet interface

#### **Related concepts**

2.12 External user memory on page 2-35.

#### **Related references**

5.9 Ethernet connector on page 5-88.

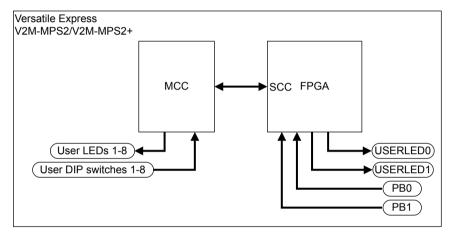

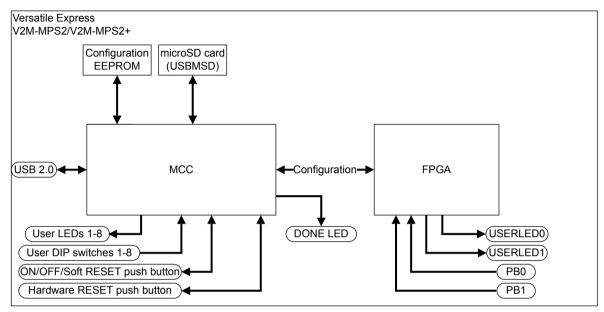

# 2.11 User switches and user LEDs

The V2M-MPS2 and V2M-MPS2+ motherboards provide a user interface that consists of user LEDs and user switches that connect to the FPGA and MCC. The FPGA image and application software define their meaning.

The board provides the following LEDs and switches:

- Two LEDs and two push buttons that connect directly to the FPGA:

- The board labels the LEDs as USERLED0 and USERLED1.

- The board labels the push buttons as *PB0* and *PB1*.

- Eight LEDs and an 8-way DIP switch that connect to the MCC.

You can write the values from these LEDs and switches to system registers inside the FPGA using a serial SCC interface.

The following diagram shows the user switches and LEDs that form the FPGA and MCC user interface.

Figure 2-11 Motherboard FPGA and MCC user interface

#### **Related concepts**

2.13 MCC FPGA serial interface on page 2-38.

#### **Related references**

1.3 Location of components on the V2M-MPS2 motherboard on page 1-15.

1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

4.4.3 SCC\_CFG1 Register on page 4-63.

4.4.4 SCC\_CFG3 Register on page 4-63.

# 2.12 External user memory

The V2M-MPS2 and V2M-MPS2+ motherboards provide external user ZBT SSRAM and PSRAM memory.

The external user memory connects to the FPGA and consists of the following:

- Two 2MB 32-bit fast single-cycle ZBT SSRAM memories:

- These connect to two independent 32-bit memory interfaces on the FPGA.

- One 4MB 32-bit fast single-cycle ZBT SSRAM memory:

- This consists of two 2MB 32-bit memories which the board configures as one 64-bit memory. They connect to one 64-bit memory interface on the FPGA.

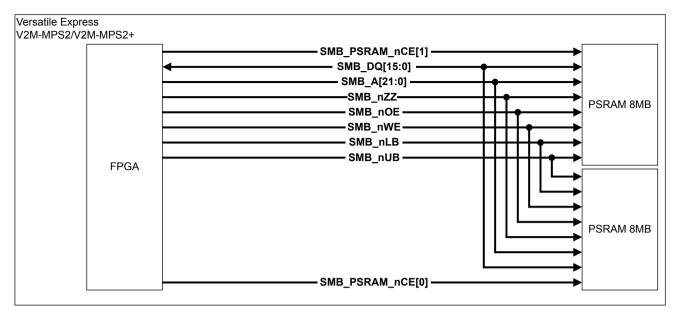

- Two 16-bit 8MB PSRAM memory:

- These supplement the ZBT SSRAM.

\_\_\_\_\_ Note \_\_\_\_\_

The 16MB PSRAM connects to the same 16-bit interface on the FPGA as the Ethernet MAC/PHY.

The MCC can pre-load the external user memory using the images.txt file before releasing reset. This enables the V2M-MPS2 and V2M-MPS2+ motherboards to use the external memory as boot RAM.

The following diagram shows the external ZBT SSRAM user memory interface.

#### 2 Hardware Description 2.12 External user memory

| Versatile Express<br>V2M-MPS2/V2M-MPS2+ |                                                                                                                                                                                                                                                                                                              |                     |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                         | SSRAM1_ADV_nBW[7:0]       SSRAM1_ADV_nBW[7:4]         SSRAM1_DQ[63:0]       SSRAM1_DQ[63:32]         SSRAM1_DQP[7:0]       SSRAM1_DQP[7:4]         SSRAM1_DQP[7:0]       SSRAM1_A[18:0]         SSRAM1_ADV_nLD       SSRAM1_ADV_nLD         SSRAM1_nOE       SSRAM1_ZZ         SSRAM1_MODE       SSRAM1_nCE1 | ZBT<br>SSRAM<br>2MB |

| FPGA                                    | SSRAM1_ADV_nBW[3:0] →<br>SSRAM1_DQ[31:0] →<br>SSRAM1_DQP[3:0] →<br>SSRAM1_A[18:0] →<br>SSRAM1_nWE →<br>SSRAM1_nOE →<br>SSRAM1_nCEN →<br>SSRAM1_nCEN →<br>SSRAM1_NODE →<br>SSRAM1_nCE1 →<br>SSRAM1_CLK0 →                                                                                                     | ZBT<br>SSRAM<br>2MB |

|                                         | SSRAM2_CLK<br>SSRAM2_ADV_nBW[3:0]<br>SSRAM2_DQ[31:0]<br>SSRAM2_DQP[3:0]<br>SSRAM2_A[18:0]<br>SSRAM2_NWE<br>SSRAM2_NWE<br>SSRAM2_ADVnLD<br>SSRAM2_NOE<br>SSRAM2_nCEN<br>SSRAM2_TCEN<br>SSRAM2_TCEN<br>SSRAM2_TCEN                                                                                             | ZBT<br>SSRAM<br>2MB |

|                                         | SSRAM3_CLK<br>SSRAM3_ADV_nBW[3:0]<br>SSRAM3_DQ[31:0]<br>SSRAM3_DQP[3:0]<br>SSRAM3_A[18:0]<br>SSRAM3_A[18:0]<br>SSRAM3_nWE<br>SSRAM3_ADVnLD<br>SSRAM3_nOE<br>SSRAM3_nCEN<br>SSRAM3_ZZ<br>SSRAM3_NODE<br>SSRAM3_nCE1                                                                                           | ZBT<br>SSRAM<br>2MB |

## Figure 2-12 ZBT SSRAM external user memory interface

The following diagram shows the external PSRAM user memory interface.

Figure 2-13 PSRAM external user memory interface

# **Related concepts**

2.10 Ethernet interface on page 2-33.

# 2.13 MCC FPGA serial interface

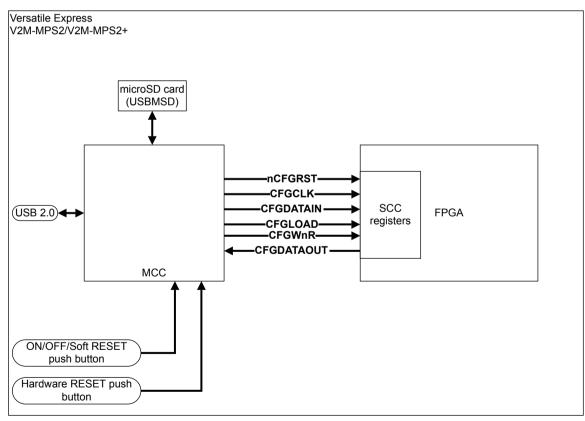

This section describes the Serial Configuration Controller (SCC) between the MCC and the FPGA.

This section contains the following subsections:

- 2.13.1 Serial Configuration Controller (SCC) on page 2-38.

- 2.13.2 SCC READ and WRITE operations on page 2-39.

- 2.13.3 SCC READ and WRITE timings on page 2-39.

### 2.13.1 Serial Configuration Controller (SCC)

The MCC uses a serial communication channel to receive from and transmit information to the FPGA on the board. You must implement a Serial Configuration Controller (SCC) in the FPGA.

### **Overview of MCC-SCC interface**

The SCC interface operates at 0.5MHz. The serial interface is similar to a memory-mapped peripheral because it has an address and data phase.

The **nCFGRST** output from the MCC loads the default configuration settings into the FPGA. **CFGLOAD** determines when WRITE DATA is complete, or when the system expects READ DATA to be ready. The MCC provides the SCC clock. **CFGWnR** changes depending on the access type. The SCC operates a 12-bit address and 32-bit data phase.

The following figure shows the MCC-SCC interface.

### Figure 2-14 MCC-FPGA serial interface

### FPGA pin assignments to implement an MCC-SCC interface

If you implement an SCC interface, you must make the following pin assignments in the FPGA:

| assign CFGCLK  | = | CLCD_PDH[13]; |  |

|----------------|---|---------------|--|

| assign nCFGRST | = | CLCD_PDH[14]; |  |

| assign | CFGLOAD      | = | CLCD PDH[15]; |

|--------|--------------|---|---------------|

| assign | CFGWnR       | = | CLCD_PDH[16]; |

|        | CFGDATAIN    | = | CLCD_PHD[17]; |

| assign | CLCD_PDH[12] | = | CFGDATAOUT;   |

|        |              |   |               |

---- Note ---

See *Application Note AN387 ARM*<sup>®</sup> *Cortex*<sup>®</sup>-*M0 Design Start SMM on V2M-MPS2* for an example scc.v file that implements these registers.

\_\_\_\_\_ Note \_\_\_\_

If the FPGA does not implement an SCC interface, ARM recommends that you tie off the **CFGDATAOUT** and **nRSTREQ** signals as follows:

- Tie the CFGDATAOUT signal from the FPGA LOW.

- Tie the **nRSTREQ** signal from the FPGA HIGH.

### **Related concepts**

2.17 Minimum design settings for motherboard operation on page 2-47.

# 2.13.2 SCC READ and WRITE operations

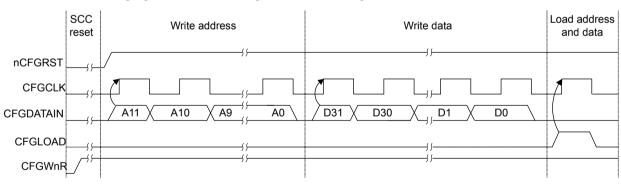

During WRITE operations, after clocking in the address and data, **CFGLOAD** loads the address and data into the SCC. The MCC clocks the WRITE DATA *Most Significant Bit* (MSB) first.

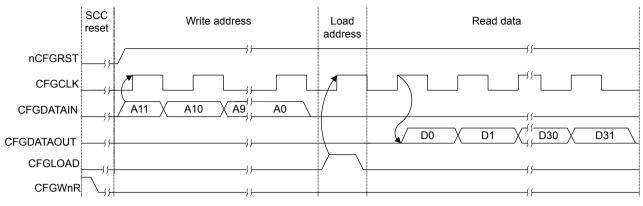

During READ operations, after clocking in the address, **CFGLOAD** loads the read address into the SCC. The SCC clocks the READ DATA *Least Significant Bit* (LSB) first.

### 2.13.3 SCC READ and WRITE timings

The following figure shows the timings for the WRITE operation.

Figure 2-15 MCC write to SCC

The following figure shows the timings for the READ operation.

Figure 2-16 MCC read from SCC

The following table shows the MCC AC timing requirements.

### Table 2-1 MCC AC timing requirements for SCC interface

| Variable                              | Time   |

|---------------------------------------|--------|

| MCC Clock to output valid time: Tov   | -500ns |

| MCC Clock to output invalid time: Toh | 500ns  |

| MCC input setup time: Tis             | 500ns  |

| MCC input hold time: Tih              | -500ns |

|                                       |        |

### **Related concepts**

2.11 User switches and user LEDs on page 2-34.

4.3 Register summary on page 4-61.

4.4 SCC register descriptions on page 4-62.

# 2.14 Power

You supply power to the motherboard from the mains supply using the on-board connector and the connector cable that ARM supplies with the board.

ARM supplies an external power supply unit which converts mains power to 12V DC which connects to the 12V connector on the board. The unit accepts mains power in the range 110V AC to 240V AC.

— Warning ——

If you supply your own external mains adaptor, it must be a Low-Power Source. Some such are marked *LPS* on their rating label. Otherwise it might be necessary to consult you adaptor supplier to ensure that it meets this criterion.

Alternatively, you can connect an external 12V DC supply, +/- 10%, directly to the 12V connector.

——— Warning —

Any external 12V DC +/- 10% power supply that is used must be a limited power source.

On-board regulators supply power to the motherboard power domains and to the FPGA power domains.

The *PWR* LED illuminates when the MCC is powered up and active.

### **Related references**

*5.10 12V power connector* on page 5-89. *FPGA current requirements* on page Appx-A-91.

# 2.15 Debug and trace

This section describes the debug and trace systems on the V2M-MPS2 and V2M-MPS2+ motherboards.

# 2.16 Overview of FPGA debug and trace systems

The V2M-MPS2 and V2M-MPS2+ motherboards provide several debug and trace interfaces:

- P-JTAG processor debug.

- F-JTAG FPGA debug.

- 16-bit parallel Trace.

- 4-bit parallel Trace.

- Serial Wire Debug (SWD).

- CMSIS-DAP FPGA debug.

—— Note —

- The availability of system debug depends on the design that you implement in the FPGA.

- The V2M-MPS2 and V2M-MPS2+ motherboards require motherboard configuration controller firmware version 2.0.1 or later to support CMSIS-DAP.

The following diagram shows a simplified view of the F-JTAG, P-JTAG, Trace, SWD, and CMSIS-DAP connections.

— Caution —

The total current limit for the four P-JTAG connectors, ARM JTAG 20, MICTOR 38, CoreSight<sup>M</sup> 20, and CoreSight<sup>M</sup> 10 is 50mA.

### Figure 2-17 Overview of motherboard debug and trace

\_\_\_\_\_ Note —

- The ILA device can be any compatible device, for example, SignalTap II.

- The processor debug device can be any compatible debugger, for example SignalTap II.

This section contains the following subsections:

- 2.16.1 F-JTAG on page 2-44.

- 2.16.2 P-JTAG on page 2-45.

- 2.16.3 4-bit Trace on page 2-45.

- 2.16.4 16-bit Trace on page 2-45.

- 2.16.5 Serial Wire Debug on page 2-45.

- 2.16.6 CMSIS-DAP FPGA debug on page 2-46.

# 2.16.1 F-JTAG

The JTAG 14 connector supports F-JTAG, FPGA debug.

The F-JTAG chain connects to the hard TAP controllers in the FPGA. The availability of F-JTAG depends on the design which you implement in the FPGA.

# **Related references**

*1.3 Location of components on the V2M-MPS2 motherboard* on page 1-15. *1.4 Location of components on the V2M-MPS2+ motherboard* on page 1-18. *5.1.1 JTAG 14 connector* on page 5-73.

## 2.16.2 P-JTAG

The V2M-MPS2 and V2M-MPS2+ motherboards provide several connectors that support P-JTAG, processor debug.

- ARM JTAG 20 connector.

- CoreSight 10 connector.

- CoreSight 20 connector.

- MICTOR 38 connector.

The availability of P-JTAG depends on the design which you implement in the FPGA.

### **Related references**

1.3 Location of components on the V2M-MPS2 motherboard on page 1-15.

1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

5.1.2 ARM JTAG 20 connector on page 5-74.

5.1.3 CoreSight<sup>™</sup> 10 connector on page 5-75.

5.1.4 CoreSight<sup>™</sup> 20 connector on page 5-75.

5.1.5 MICTOR 38 connector on page 5-76.

# 2.16.3 4-bit Trace

The CoreSight 20 connector supports 4-bit Trace on the V2M-MPS2 and V2M-MPS2+ motherboards.

The availability of 4-bit Trace depends on the design which you implement in the FPGA.

### **Related references**

1.3 Location of components on the V2M-MPS2 motherboard on page 1-15.

1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

5.1.4 CoreSight<sup>™</sup> 20 connector on page 5-75.

### 2.16.4 16-bit Trace

The MICTOR 38 connector supports 16-bit Trace on the V2M-MPS2 and V2M-MPS2+ motherboards.

The availability of 16-bit Trace depends on the design which you implement in the FPGA.

### **Related references**

*1.3 Location of components on the V2M-MPS2 motherboard* on page 1-15. *1.4 Location of components on the V2M-MPS2+ motherboard* on page 1-18. *5.1.5 MICTOR 38 connector* on page 5-76.

# 2.16.5 Serial Wire Debug

The V2M-MPS2 and V2M-MPS2+ motherboards provide several connectors that support Serial Wire Debug (SWD).

- ARM JTAG 20 connector.

- CoreSight 10 connector.

- CoreSight 20 connector.

- MICTOR 38 connector.

The availability of SWD depends upon the design which you implement in the FPGA.

# **Related references**

1.3 Location of components on the V2M-MPS2 motherboard on page 1-15. 1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

5.1.2 ARM JTAG 20 connector on page 5-74.

5.1.3 CoreSight<sup>™</sup> 10 connector on page 5-75.

5.1.4 CoreSight<sup>™</sup> 20 connector on page 5-75.

5.1.5 MICTOR 38 connector on page 5-76.

# 2.16.6 CMSIS-DAP FPGA debug

The USB 2.0 Full Speed ports on the V2M-MPS2 and V2M-MPS2+ motherboards support CMSIS-DAP debug.

A workstation running a debugger connects to the CMSIS-DAP port which connects to the MCC. The MCC implements CMSIS-DAP which runs over JTAG connection to the debug access port in the FPGA.

The availability of CMSIS-DAP depends on the design that you implement in the FPGA. The V2M-MPS2 and V2M-MPS2+ motherboards require motherboard configuration software version 2.0.1 or later to support CMSIS-DAP.

# **Related concepts**

2.5 USB 2.0 Full Speed interface on page 2-28.

# 2.17 Minimum design settings for motherboard operation

You must implement a minimum amount of RTL in the FPGA for the V2M-MPS2 motherboard or V2M-MPS2+ motherboard to operate correctly.

You must tie off the following FPGA signals to generate the minimum RTL in the FPGA for correct operation:

- 1. Set the following signals to the inactive HIGH state:

- SMB PSRAM nce[1:0].

- SMB\_ETH\_nCS.

- SSRAM1\_nCE1.

- SSRAM2\_nCE1

- SSRAM3\_nCE1

- 2. Set the SMB chip select to the inactive HIGH state by tying the chip selects SMB\_nCS to 0b11111111.

- 3. Set the CFGDATAOUT signal to the inactive LOW state by tying NAND\_D[5] to 0b0.

— Note -

- Note -

This informs the MCC that the motherboard does not implement any of its features.

4. Set the **nRSTREQ** to the inactive HIGH state by tying **NAND\_D**[7] to 0b1.

This prevents **nRSTREQ** from generating a reset. **nRSTREQ** is usually a system-wide master soft reset signal that is both generated and observed by the JTAG debug box.

\_\_\_\_\_ Note \_\_\_\_\_

ARM recommends that you tie all unused pins to their inactive states.

### **Related concepts**

2.13.1 Serial Configuration Controller (SCC) on page 2-38.

# Chapter 3 Configuration

This chapter describes the powerup and configuration process of the Versatile Express V2M-MPS2 and V2M-MPS2+ motherboards.

It contains the following sections:

- 3.1 Overview of the configuration process on page 3-49.

- *3.2 Configuration system* on page 3-51.

- 3.3 Powerup and configuration process on page 3-52.

- *3.4 Reset push buttons* on page 3-54.

- 3.5 Configuration files on page 3-55.

# 3.1 Overview of the configuration process

The MCC, in association with the microSD card, configures the V2M-MPS2 and V2M-MPS2+ motherboards during powerup or reset. When the configuration process starts after application of power or a press of one of the RESET buttons, the configuration process completes without further intervention from the user.

The microSD card stores the board configuration files, including the board.txt and config.txt files. You can access the microSD card as a *Universal Serial Bus Mass Storage Device* (USBMSD)

The MCC:

- Reads the FPGA image from the microSD card and loads it into the FPGA.

- Sets the board oscillator frequencies using values from the board.txt file.

- Configures the FPGA SCC registers using values from the board.txt file

- Pre-loads the SRAM with the boot image that the images.txt file defines.

### —— Note —

You must make the following pin assignments in the FPGA to enable the MCC to pre-load the boot image into the SRAM.

| config_spiclk               | = | CLCD_PDL[6];<br>CLCD_PDL[8]; |

|-----------------------------|---|------------------------------|

| config_spidi<br>CLCD_PDL[7] | = | config_spido;                |

At the start of the configuration process, the MCC reads the contents of the configuration EEPROM. The EEPROM contains the following information:

- Board HBI number.

- Board revision.

- Board variant.

- Number of FPGAs.

- Note

• The names of the current images in 8.3 format and the file creation dates.

The HBI number is a unique code that identifies the board. The root directories of the EEPROM and the microSD card contain subdirectories in the form *HBIBoardNumberBoardrevision*, for example HBI0263B.

There are two stages in programming and configuring the images into the FPGA:

1. The MCC compares the file names and dates in the EEPROM to the information in the configuration files in the microSD card. The microSD card contains the FPGA images and information about their creation dates.

If the microSD card contains an updated image, the MCC validates it and updates the information in the EEPROM.

—— Note —

- The USB 2.0 Full Speed connection to the MCC supports MSD class enabling *Drag-and-Drop* for transferring new images to the microSD card. The microSD card appears in the file system as a device with removable storage.

- The HDD LED illuminates during read or write accesses to the microSD card.

3. The MCC illuminates the DONE LED to indicate that configuration is complete.

<sup>2.</sup> The MCC loads the FPGA image into the FPGA.

# **Related concepts**

2.5 USB 2.0 Full Speed interface on page 2-28.

# 3.2 Configuration system

The V2M-MPS2 and V2M-MPS2+ motherboards provide hardware infrastructure to enable board configuration during powerup or reset.

The following diagram shows the motherboard configuration system.

### Figure 3-1 Motherboard configuration system

### Configuration port connected to an external workstation

If you connect an external workstation to the MCC USB 2.0 Full Speed port, you can access the configuration memory in the microSD card. You can then edit and copy configuration files and software images to the SD card.

# **Related concepts**

- 2.5 USB 2.0 Full Speed interface on page 2-28.

- 3.5.2 config.txt generic motherboard configuration file on page 3-56.

- 3.5.3 Contents of the MB directory on page 3-56.

- 3.5.4 Contents of the SOFTWARE directory on page 3-57.

- 3.5.1 Overview of configuration files and microSD card directory structure on page 3-55.

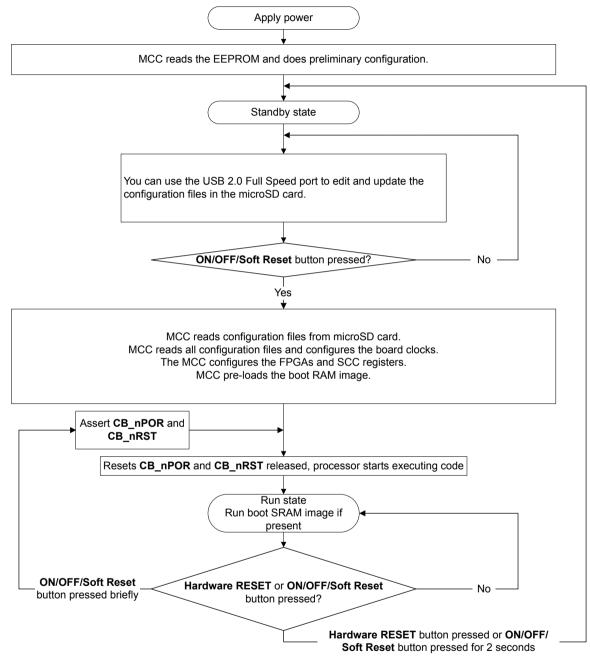

# 3.3 Powerup and configuration process

The power push buttons and configuration files control the sequence of events of the V2M-MPS2 and V2M-MPS2+ motherboard powerup and configuration process.

The following figure shows the powerup and configuration process.

### Figure 3-2 Powerup and configuration sequence

The motherboard powerup and configuration sequence is:

- 1. The board applies power to the system.

- 2. The MCC powers the EEPROM and reads it to determine the HBI identification code for the board.

- 3. The system enters standby mode.

- 4. The system enables the microSD memory card and you can connect a workstation to the MCC USB 2.0 Full Speed port to edit existing configuration files or *Drag-and-Drop* new configuration files.

- 5. The system stays in standby state until you press the ON/OFF/Soft RESET push button.

- 6. The system loads the board configuration file:

- The MCC reads the generic config.txt file.

- The MCC searches the microSD card MB directory for the HBI0263x subdirectory that matches the board HBI code from the board EEPROM.

- 7. The next steps depend on the configuration files:

- If the MCC finds configuration subdirectories that match the HBI code of the motherboard, configuration continues and the MCC reads the board.txt file.

- If the MCC does not find the correct configuration files, it records the failure to a log file on the microSD card. Configuration stops and the system re-enters standby state.

- 8. The MCC measures the board power supplies.

- 9. The MCC configures the board clocks and FPGA SCC registers.

- 10. If the MCC finds new software images, it loads them into the SRAM through the FPGA.

- 11. The MCC releases the system resets nPOR and nRST, the system enters RUN state.

- 12. Normal operation continues until a new event occurs:

### **Related concepts**

3.5.2 config.txt generic motherboard configuration file on page 3-56.

- 3.5.3 Contents of the MB directory on page 3-56.

- 3.5.4 Contents of the SOFTWARE directory on page 3-57.

- 3.5.1 Overview of configuration files and microSD card directory structure on page 3-55.

# 3.4 Reset push buttons

The V2M-MPS2 and V2M-MPS2+ motherboards provide two push buttons which initiate reset and configuration. The two reset push buttons are the ON/OFF/Soft RESET and the Hardware RESET buttons. This section describes the use and functions of these push buttons.

This section contains the following subsections:

- 3.4.1 ON/OFF/Soft RESET button on page 3-54.

- 3.4.2 Hardware RESET button on page 3-54.

### 3.4.1 ON/OFF/Soft RESET button

The V2M-MPS2 and V2M-MPS2+ motherboards provide an ON/OFF/Soft RESET push button that enables you to perform a software reset of the system.

You initiate a software reset of the system by briefly pressing the *ON/OFF/Soft RESET* button during runtime. The MCC performs a software reset of the FPGA and resets the devices on the board. It does not perform a full reconfiguration of the FPGA.

The software reset sequence is as follows:

1. You briefly press the ON/OFF/Soft RESET button.

— Caution —

If you press and hold the *ON/OFF/Soft RESET* button for more than two seconds, the system enters the Standby State in the same way as pressing the *Hardware RESET* button.

- 2. The MCC asserts the **nRST** reset signal. It might also assert **nPOR** but this depends on the setting of the variable *ASSERTNPOR* in the configuration file config.txt.

- 3. The MCC releases **nPOR** if it is active depending on the setting of the variable ASSERTNPOR in the configuration file config.txt.

- 4. The MCC releases **nRST**.

- 5. The motherboard enters the run state.

------ Note -----

The MCC does not read the configuration files or perform a board reconfiguration as a result of a software reset.

### **Related references**

1.3 Location of components on the V2M-MPS2 motherboard on page 1-15. 1.4 Location of components on the V2M-MPS2+ motherboard on page 1-18.

# 3.4.2 Hardware RESET button

The V2M-MPS2 and V2M-MPS2+ motherboards provide a Hardware RESET push button that enables you to perform a hardware reset of the system.

You can change the operation of the board from ON to Standby by briefly pressing this button. This switches off the power to the board and resets the system to the default values.

If you then press the ON/OFF/Soft RESET push button, the system performs a full configuration and enters the run state.

### **Related references**

*1.3 Location of components on the V2M-MPS2 motherboard* on page 1-15. *1.4 Location of components on the V2M-MPS2+ motherboard* on page 1-18.

# 3.5 Configuration files

This section describes the V2M-MPS2 and V2M-MPS2+ motherboard configuration files in the microSD card which control the board powerup and configuration process.

This section contains the following subsections:

- 3.5.1 Overview of configuration files and microSD card directory structure on page 3-55.

- 3.5.2 config.txt generic motherboard configuration file on page 3-56.

- 3.5.3 Contents of the MB directory on page 3-56.

- *3.5.4 Contents of the SOFTWARE directory* on page 3-57.

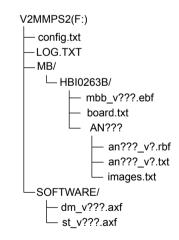

### 3.5.1 Overview of configuration files and microSD card directory structure

Because the motherboard microSD card is non-volatile memory, it is only necessary to load new configuration files if you change the system configuration. The microSD card contains default configuration files.

If you connect a workstation to the MCC USB 2.0 Full Speed port, the configuration memory device, the SD card, appears as a *USB Mass Storage Device* (USBMSD) and you can add, edit, or delete files.

You can use a standard text editor that produces DOS line endings to read and edit the board configuration files.

The following figure shows a typical example of the directory structure in the microSD card memory.

### — Caution –

Files names and directory names are in 8.3 format:

- File names that you generate must be in lower case.

- Directory names must be in upper case.

- All configuration files must end in DOS line endings (0x0D/0x0A).

### Figure 3-3 Example USBMSD directory structure

The directory structure and file name format ensure that each image is matched to the correct target device defined in the board configuration EEPROM.

- config.txt is the generic configuration file for all motherboards. This file applies to all Versatile Express motherboards including the V2M-MPS2 and V2M-MPS2+ motherboards.

- The MB directory contains subdirectories for any motherboard variants that might be present in the system. The subdirectory names match the HBI codes for the specific motherboard variants. The files in this directory contain clock, register, and other settings for the motherboard.

- The SOFTWARE directory contains application files that the MCC can load into the ZBT SSRAM or PSRAM on the board. The images.txt file defines the file that the MCC loads.

### **Related concepts**

2.5 USB 2.0 Full Speed interface on page 2-28.

3.5.2 config.txt generic motherboard configuration file on page 3-56.

3.5.3 Contents of the MB directory on page 3-56.

3.5.4 Contents of the SOFTWARE directory on page 3-57.

### 3.5.2 config.txt generic motherboard configuration file

You can use the V2M-MPS2 or V2M-MPS2+ motherboard USB 2.0 Full Speed port to update the generic Versatile Express configuration file config.txt from your workstation to the root directory of the microSD card.

The following example shows a configuration file that you can load into the configuration flash memory.

- Colons (:) indicate the end of commands and must be separated by a space character (0x20) from the value fields.

- Semicolons (;) indicate comments.

- Note

TITLE: Versatile Express V2M-MPS2 configuration file

```

[CONFIGURATION]<br/>AUTORUN: FALSE<br/>AUTORUN: FALSE<br/>RTC: FALSE;Auto Run from power on<br/>;Delay in seconds to wait for key press to stop bootup<br/>;TRUE = Enable RTC, FALSE = Disable RTCASSERTNPOR: TRUE<br/>WDTRESET: NONE;External resets assert nPOR<br/>;Watchdog reset options NONE/RESETMB/RESETDBUSB_REMOTE: TRUE<br/>WSB_REMOTE: TRUE;Selects remote command via USBMACADDRESS: 0xFFFFFFFFFF;MAC Address

```

### 3.5.3 Contents of the MB directory

The V2M-MPS2 and V2M-MPS2+ motherboard MB directories contain a configuration HBI subdirectory that matches the HBI code of the board.

The HBI subdirectory contains:

- A file of the form *mbb vxxx.ebf*. This is an MCC BIOS image.

- A board.txt file that defines the MCC bios image.

- An application-specific subdirectory that contains the following board configuration files:

- Image files for the FPGA and MCC on the board. These have .rbf extensions.

- An images.txt file that defines the .axf files that the MCC loads into external memory during configuration.

- An application note .txt file that defines the number of FPGAs on the board, the number of oscillators and their frequencies, FPGA and MCC image files, and details of the SCC registers.

The following example shows a typical V2M-MPS2 or V2M-MPS2+ motherboard configuration board.txt file.

BOARD: HBI0263 TITLE: Motherboard configuration file [MCCS] MBBIOS mbb\_v201.ebf ;MB BIOS IMAGE [APPLICATION NOTE] ;Please select the required processor APPFILE: AN382\an382\_v2.txt ; - Cortex-M0 ;APPFILE: AN383\an383\_v2.txt - Cortex-M0+ APPFILE: AN384\an384\_v2.txt - Cortex-M1 APPFILE: AN385\an385\_v2.txt - Cortex-M3 ;APPFILE: AN386\an386\_v2.txt Cortex-M4 APPFILE: AN387\an387\_v2.txt Cortex-M0 Design Start ;APPFILE: AN399\an399\_v2.txt - Cortex-M7

;APPFILE: AN400\an400\_v2.txt

The following example shows a typical V2M-MPS2 or V2M-MPS2+ motherboard application note .txt file.

BOARD: HBI0263 TITLE: Application Note File [FPGAS] ;Total Number of FPGAS (Max : 1) TOTALFPGAS: 1 FØFILE: an385\_v2.rbf FØMODE: FPGA ;FPGA0 Filename ;FPGA0 Programming Mode [OSCCLKS] TOTALOSCCLKS: 3 OSC0: 50.0 OSC1: 24.576 OSC2: 25.0 ;OSC0 System clock in MHz ;OSC1 AACI clock in MHz ;OSC2 MISC clock in MHz [SCC REGISTERS] TOTALSYSCONS: 1 ;Total Number of SYSCON registers defined SYSCON: 0x000 0x0000001 ;SCC enable ZBT remap

The following example shows a typical V2M-MPS2 or V2M-MPS2+ motherboard images.txt file.

```

TITLE: Versatile Express Images Configuration File

[IMAGES]

TOTALIMAGES: 1 ;Number of Images (Max : 32)

IMAGE0ADDRESS:0x00000000 ;Please select the required executable program

IMAGE0FILE: \SOFTWARE\dm_v111.axf ; - demo

;IMAGE0FILE: \SOFTWARE\st_v111.axf ; - selftest

```

The following example shows the use of a binary file as an alternative to generating a .axf file.

TITLE: Versatile Express Images Configuration File

| [IMAGES]<br>TOTALIMAGES: 1     | ;Number of Images (Max : 32)                   |

|--------------------------------|------------------------------------------------|

| IMAGE0ADDRESS:0x00000000       | ;Please select the required executable program |

| IMAGE0FILE: \SOFTWARE\test.bin | ;                                              |

.axf and .elf files are treated as elf files. All other files are treated as binary.

### 3.5.4 Contents of the SOFTWARE directory

The SOFTWARE directory contains applications that you can load into the ZBT SSRAM or PSRAM memory.

You can create applications and load them into the RAM on the motherboard. Application images are typically boot images or demo programs and have a .axf extension.

Typical applications in this directory are:

- dm\_v102.axf board demonstration software.

- st\_v103.axf board test software.

- user.axf user test software.

# Chapter 4 Programmers Model

This chapter describes the programmers model of the Versatile Express V2M-MPS2 and V2M-MPS2+ motherboards.

It contains the following sections:

- 4.1 About this programmers model on page 4-59.

- 4.2 Memory map on page 4-60.

- *4.3 Register summary* on page 4-61.

- 4.4 SCC register descriptions on page 4-62.

- 4.5 System configuration registers on page 4-68.

# 4.1 About this programmers model

The following information applies to the SCC registers and to the system configuration registers or SYS\_CFG registers:

- The base address is not fixed, and can be different for any particular system implementation. The offset of each register from the base address is fixed.

- Do not attempt to access reserved or unused address locations. Attempting to access these locations can result in UNPREDICTABLE behavior.

- Unless otherwise stated in the accompanying text:

- Do not modify undefined register bits.

- Ignore undefined register bits on reads.

- All register bits are reset to a logic 0 by a system or powerup reset.

- Table 4-1 V2M-MPS2 and V2M-MPS2+ SCC register summary on page 4-61 describes register access type as follows:

RW: Read and write.

RO: Read only.

WO: Write only.

# 4.2 Memory map

The image that you load into the FPGA on the V2M-MPS2 or V2M-MPS2+ motherboard determines the board memory map. See the relevant SMM Application Note for an example memory map for the motherboard.

# 4.3 Register summary

This section summarizes the V2M-MPS2 and V2M-MPS2+ SCC registers and system configuration registers characteristics.

The following table shows the registers in offset order from the base memory address.

| Table 4-1 | V2M-MPS2 | and V2M-MPS2- | + SCC register | summary |

|-----------|----------|---------------|----------------|---------|

|-----------|----------|---------------|----------------|---------|

| Offset        | Name            | Туре | Reset      | Width | Comment                                                                                                                    |

|---------------|-----------------|------|------------|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0x000         | SCC_CFG0        | RW   | 0x00000000 | 32    | Remaps block RAM to ZBT.                                                                                                   |

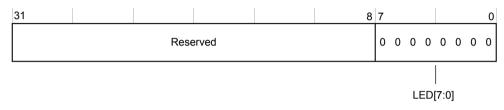

| 0x004         | SCC_CFG1        | RW   | 0x00000000 | 32    | Controls the MCC user LEDs.                                                                                                |

| 0x008         | -               | -    | -          | -     | Reserved. Do not write to or read from this register.                                                                      |

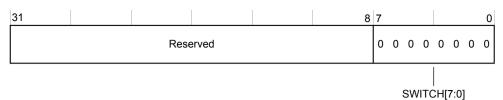

| 0x00C         | SCC_CFG3        | RO   | 0x00000000 | 32    | Denotes the state of the MCC user switches.                                                                                |

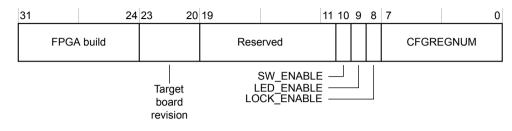

| 0x010         | SCC_CFG4        | RO   | 0x00000000 | 32    | Denotes the board revision.                                                                                                |

| 0x014 - 0x09C | -               | -    | -          | -     | Reserved. Do not write to or read from these registers                                                                     |

| 0x0A0         | SYS_CFGDATA_RTN | RO   | 0x00000000 | 32    | This is one oUser data return register for reads from board peripherals.                                                   |

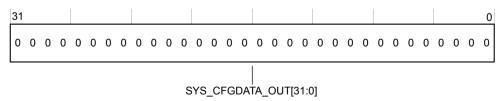

| 0x0A4         | SYS_CFGDATA_OUT | RW   | 0x00000000 | 32    | User data output register for writes to board peripherals.                                                                 |

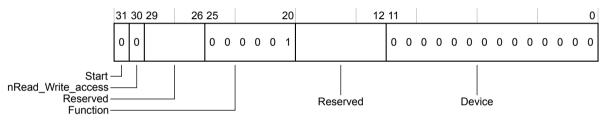

| 0x0A8         | SYS_CTRL        | RW   | 0x00100000 | 32    | Control register. Controls read and write operations.                                                                      |

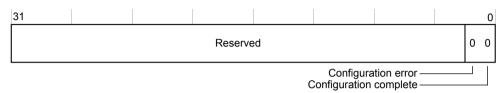

| 0x0AC         | SYS_CFGSTAT     | RO   | 0x00000000 | 32    | Status register. Shows status of read and write operations.                                                                |

| 0x0AD - 0x0FC | -               | -    | -          | -     | Reserved. Do not write to or read from these registers.                                                                    |

| 0x100         | SCC_DLL         | RO   | 0xFFFC0000 | 32    | DLL Lock Register                                                                                                          |

| 0x104 - 0xFF7 | -               | -    | -          | -     | Reserved. Do not write to or read from these registers                                                                     |